One-transistor dynamic random access memory (DRAM) unit based on silicon-germanium silicon heterojunction, and method for preparing one-transistor DRAM unit

A single-transistor, heterojunction technology, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of small difference, unfavorable DRAM working stability, high working voltage of transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

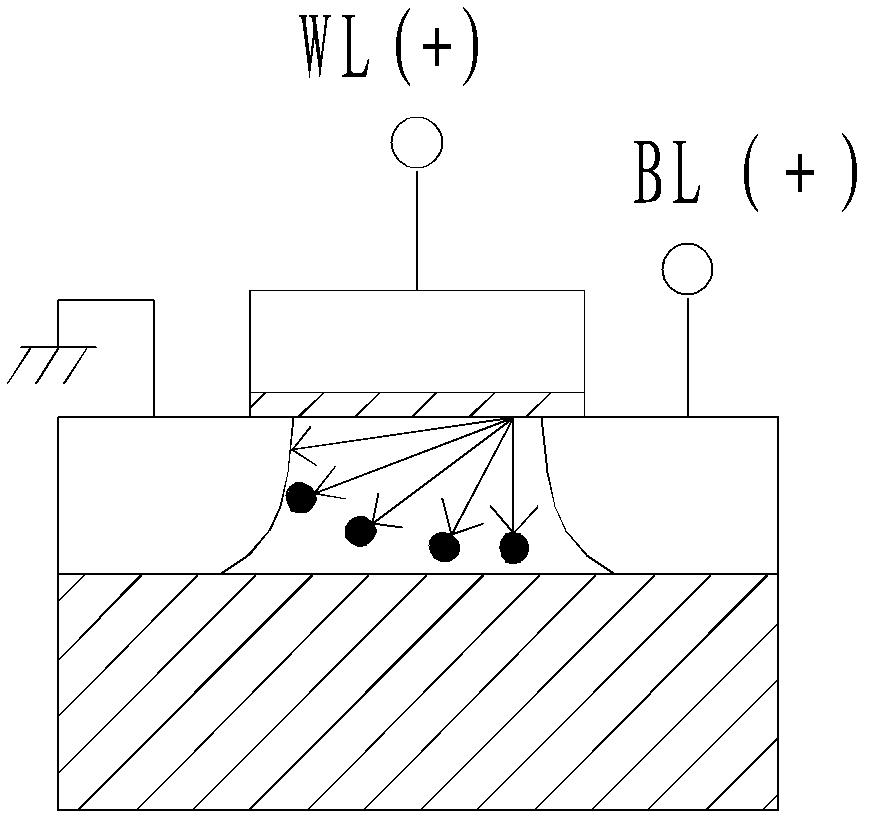

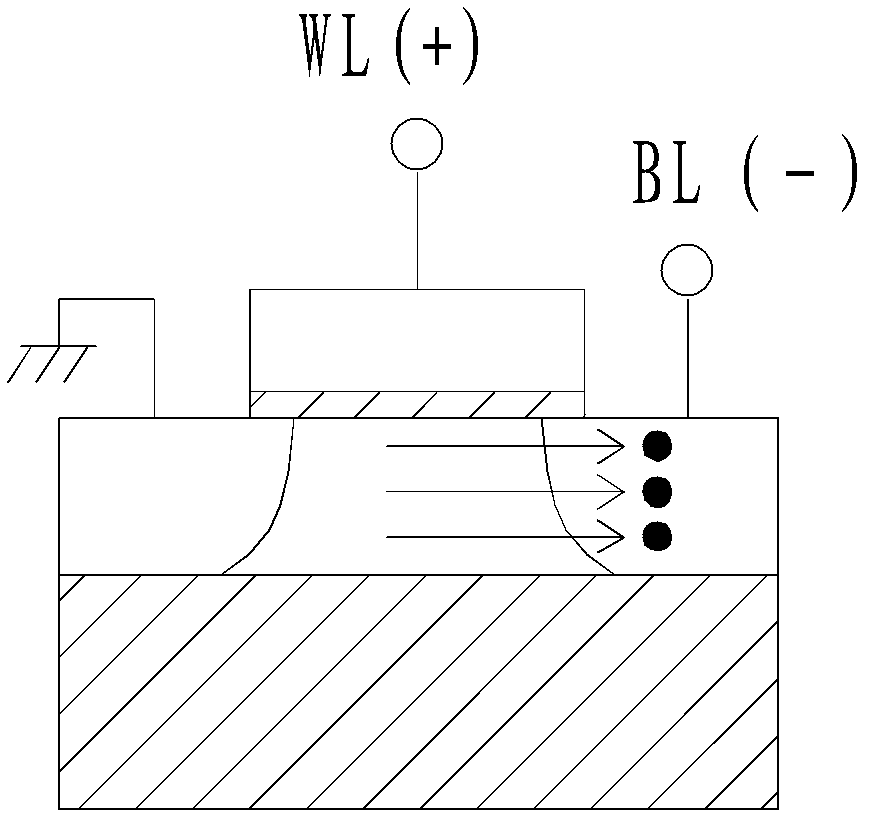

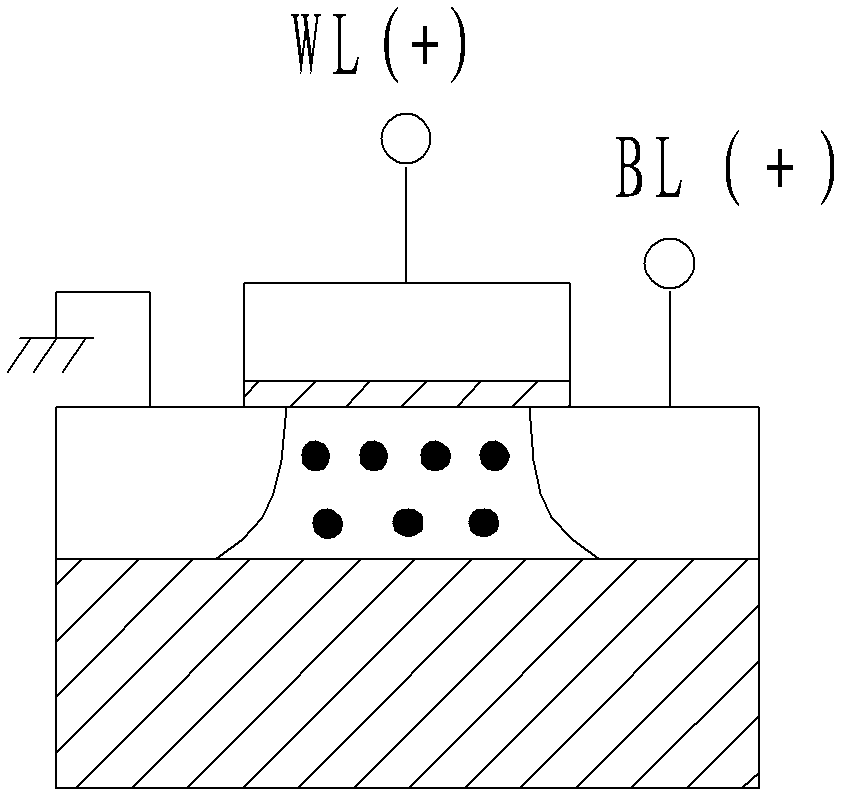

[0024] 1T-DRAM is generally a SOI (silicon on insulator) floating body (floating body) transistor. When charging its body region, it completes the write "1" operation through the accumulation of holes in the body region. At this time, due to the hole in the body region Accumulated to cause the substrate effect, resulting in a decrease in the threshold voltage of the transistor. When the body region is discharged, the hole accumulated in the body region is discharged through the body drain or the body-source PN junction forward bias (forward bias) to complete the write "0" operation, and the substrate effect disappears at this time. The threshold voltage returns to normal. The turn-on current increases. The read operation is to read the source-leakage current when the transistor is on. Since the threshold voltages of the "1" and "0" states are different, the source-leakage currents of the two are also different. When the source-leakage current is large, it means read When the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com