External clock synchronization circuit of switching power supply

A switching power supply and external synchronization technology, which is applied in the direction of electrical components, automatic power control, output power conversion devices, etc., can solve the problems of frequency jitter, circuit complexity, and long time for external synchronization of clocks, etc., to achieve accurate transmission, circuit The effect of simple structure and shortened external synchronization time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention is described in further detail below in conjunction with accompanying drawing.

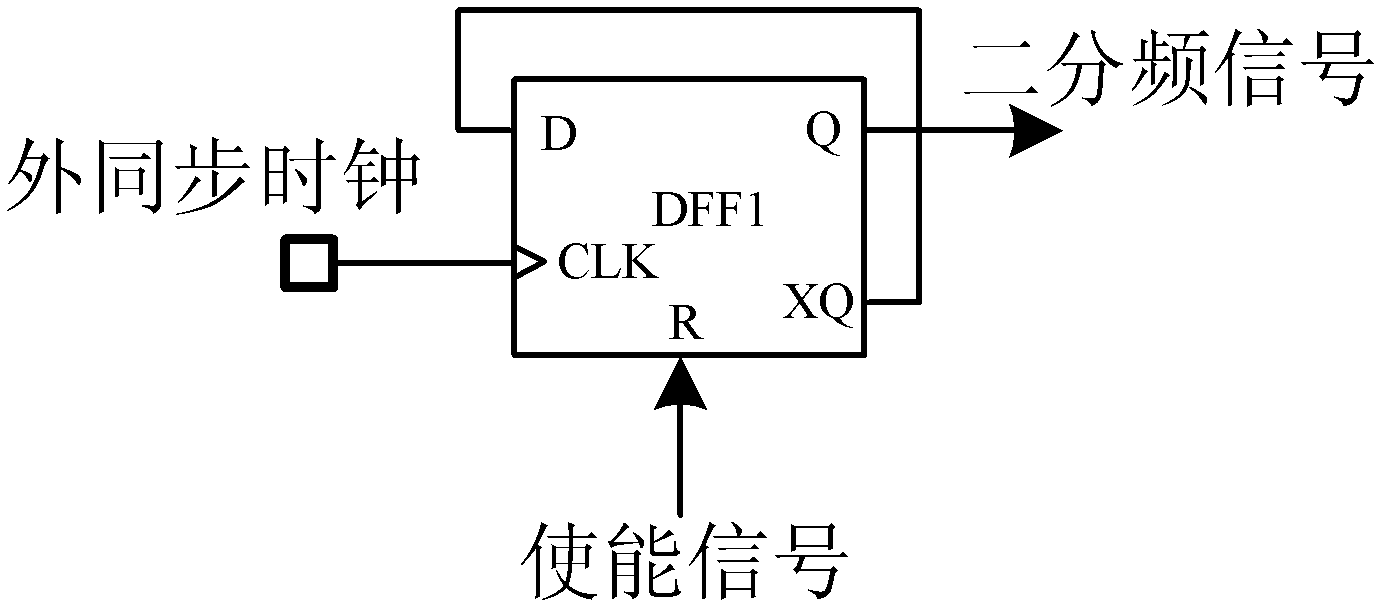

[0022] refer to figure 1 , The clock external synchronization circuit of the present invention includes a frequency division circuit 1 , a frequency upper limit detection circuit 2 , a frequency lower limit detection circuit 3 , an external synchronization stop detection circuit 4 and a frequency selection circuit 5 . After the external synchronous clock is divided by 2 into a square wave signal with a duty ratio of 50%, it is connected to the frequency lower limit detection circuit 2 and the frequency upper limit detection circuit 3 to detect whether the frequency of the external synchronous clock is at the preset value interval; the input terminal of the external synchronous stop detection circuit 4 is connected to the external synchronous clock, and the control signal k3 output by the output terminal is connected to the frequency lower limit detection circuit 3, so ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com