DRAM (Dynamic Random Access Memory) source synchronization test method and circuit

A technology for testing circuits and testing methods, applied in static memory, instruments, etc., can solve the problems of complex testing methods and low reliability in the background technology, and achieve the effects of good reliability and easy testing operations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

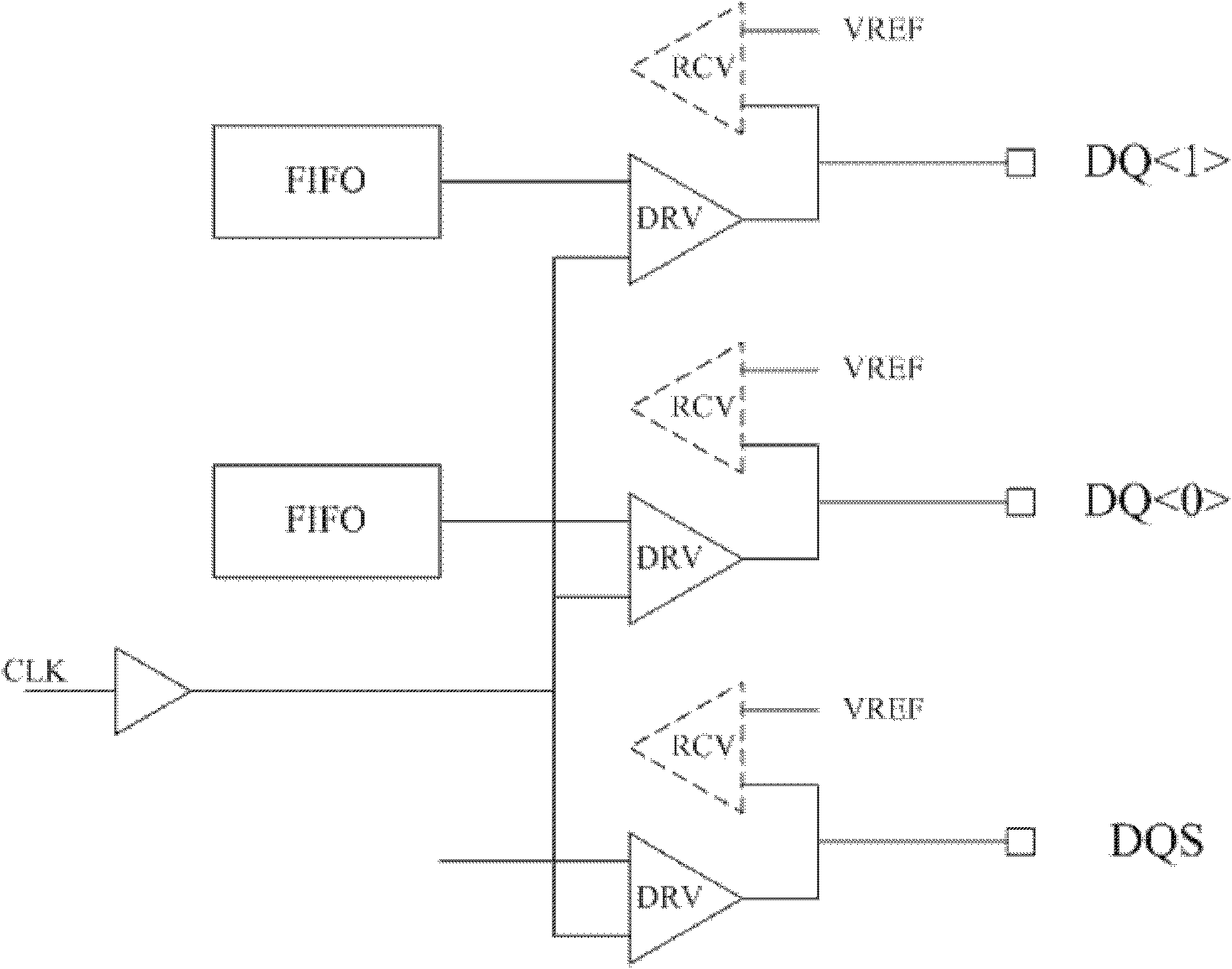

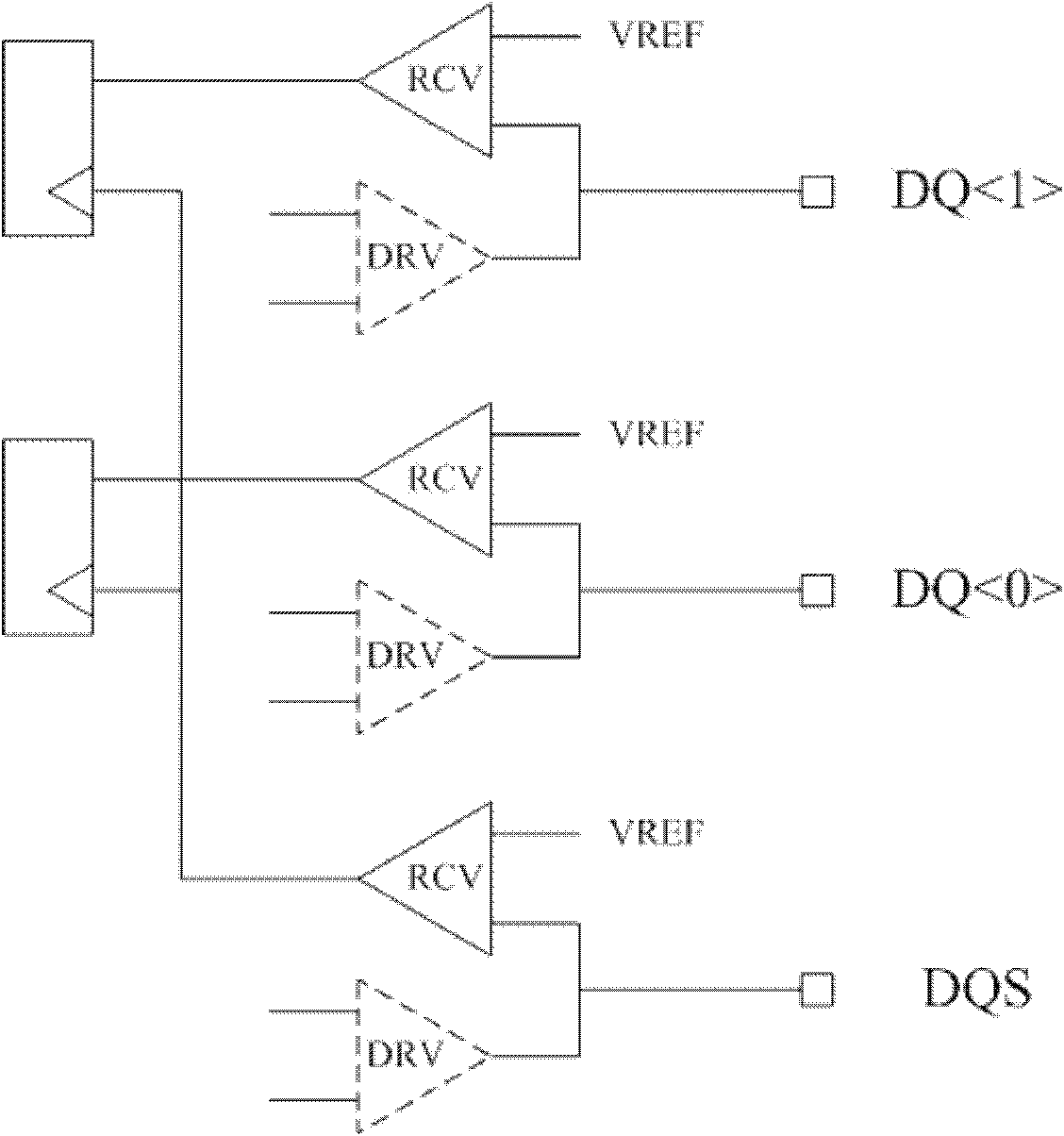

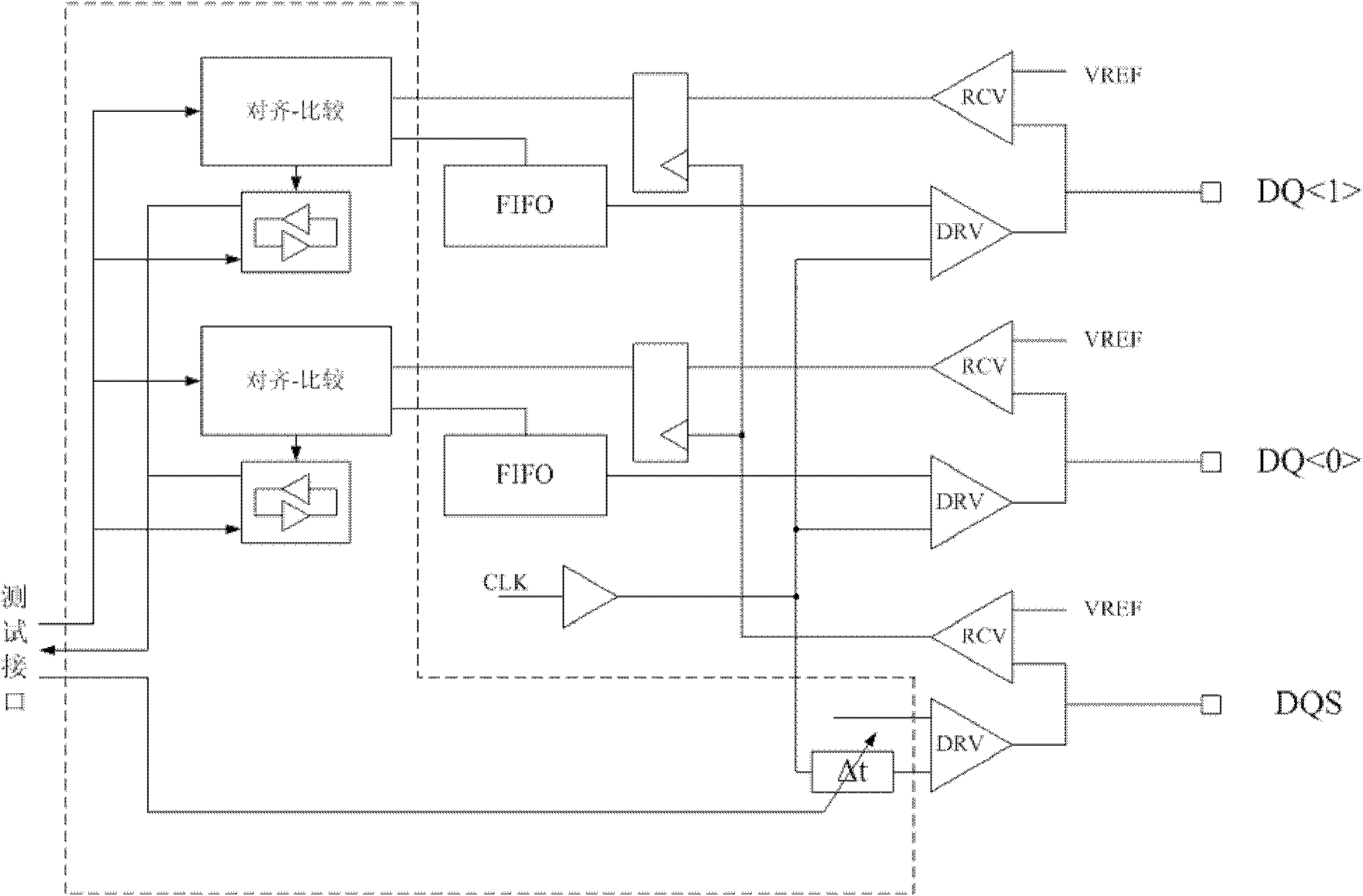

[0032] The invention provides an additional test circuit inside the DRAM, and this circuit can effectively reconstruct the source synchronous test function that the test machine cannot realize. When the circuit is activated during production testing, it will log any violations of the tDQSQ and tQH specifications. The results can be read out via the test mode interface and used for later post-processing or decision making.

[0033] The invention is a circuit which can accurately measure the source synchronization time parameter integrated in the DRAM, and whether the parameter conforms to the standard can be tested by a single operation. When the test circuit is activated, the driving circuit and the receiving circuit of the DQ pin and the DQS pin are turned on at the same time. The test circuit includes an adjustable delay unit, which can move the DQS edge relative to the DQ edge. The adjustable delay unit is located before the DQS pin drive circuit; the adjustable delay unit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com