Timer device comprising advanced reduced instruction set computer machine (ARM) and field programmable gate array (FPGA) and implementation method thereof

A timer and timing technology, which is applied to program control and electrical program control in sequence/logic controllers, can solve the problems of execution speed influence, large circuit scale, and heavy maintenance workload, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

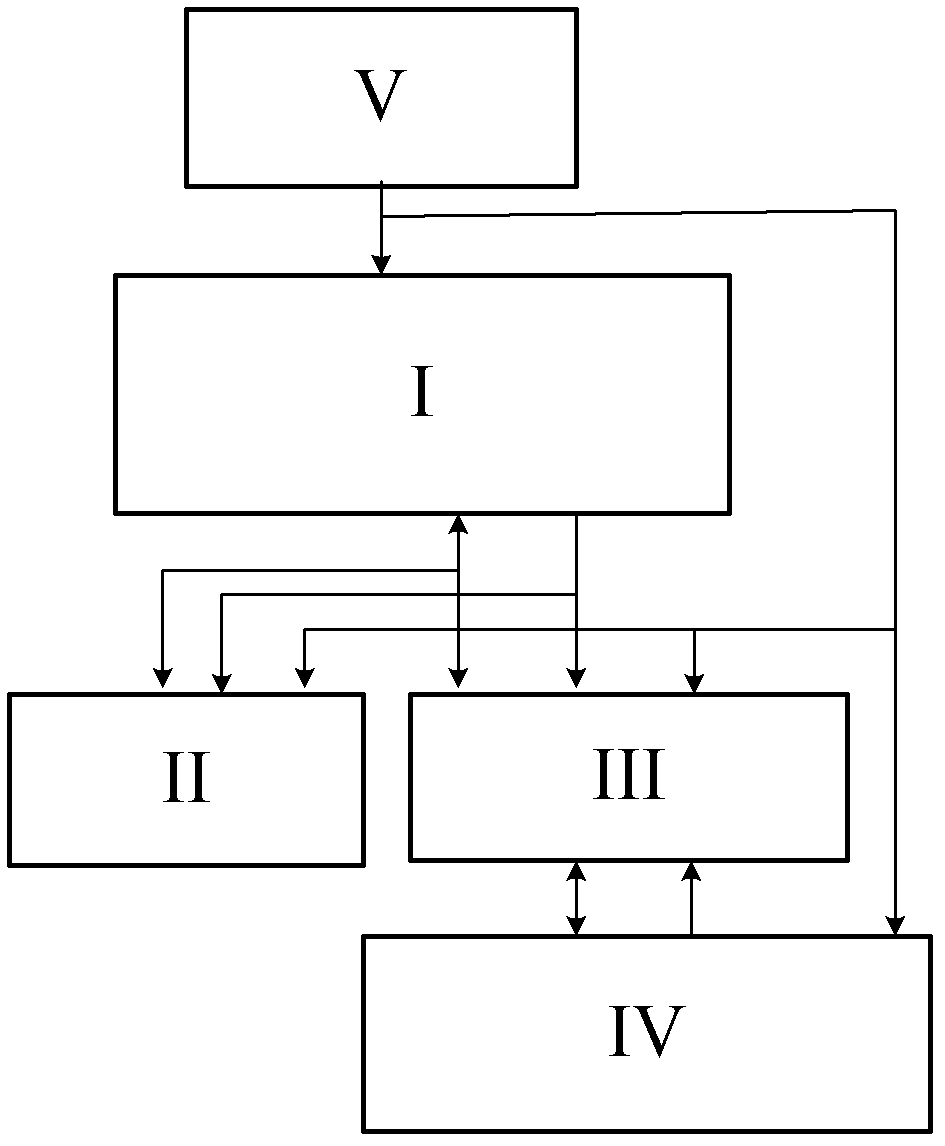

[0145] A timer device composed of ARM+FPGA, such as figure 1 As shown, the timer device includes ARM control module Ⅰ, memory module Ⅱ, FPGA timer module Ⅳ, dual-port RAM module Ⅲ and power supply module Ⅴ; ARM control module Ⅰ is connected with memory module Ⅱ and dual-port RAM module Ⅲ respectively , the FPGA timer module IV is connected to the dual-port RAM module III, and the power module V converts the external power supply into a voltage that meets the requirements through the voltage circuit, which is ARM control module I, memory module II, dual-port RAM module III and FPGA timer module ⅣProvide transformed DC power supply;

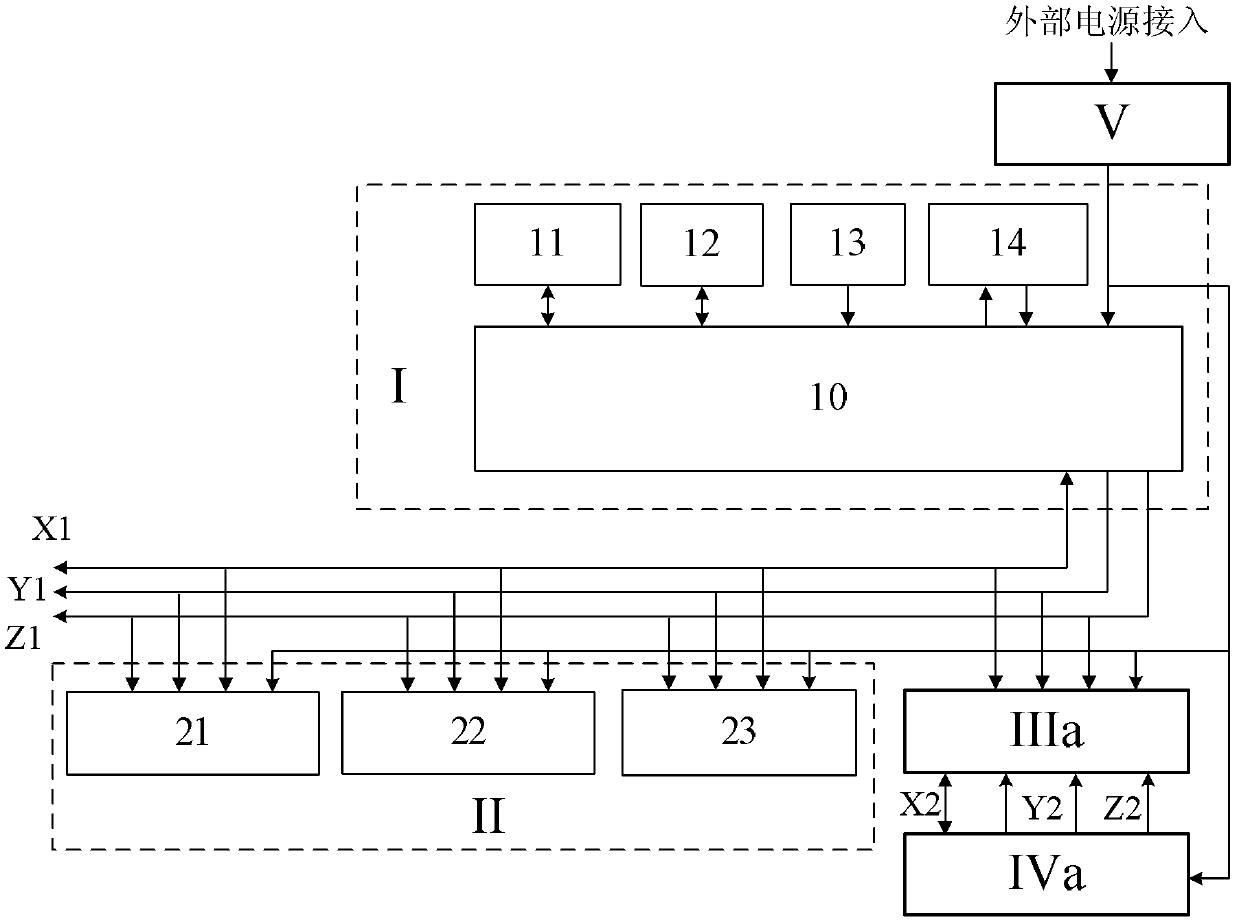

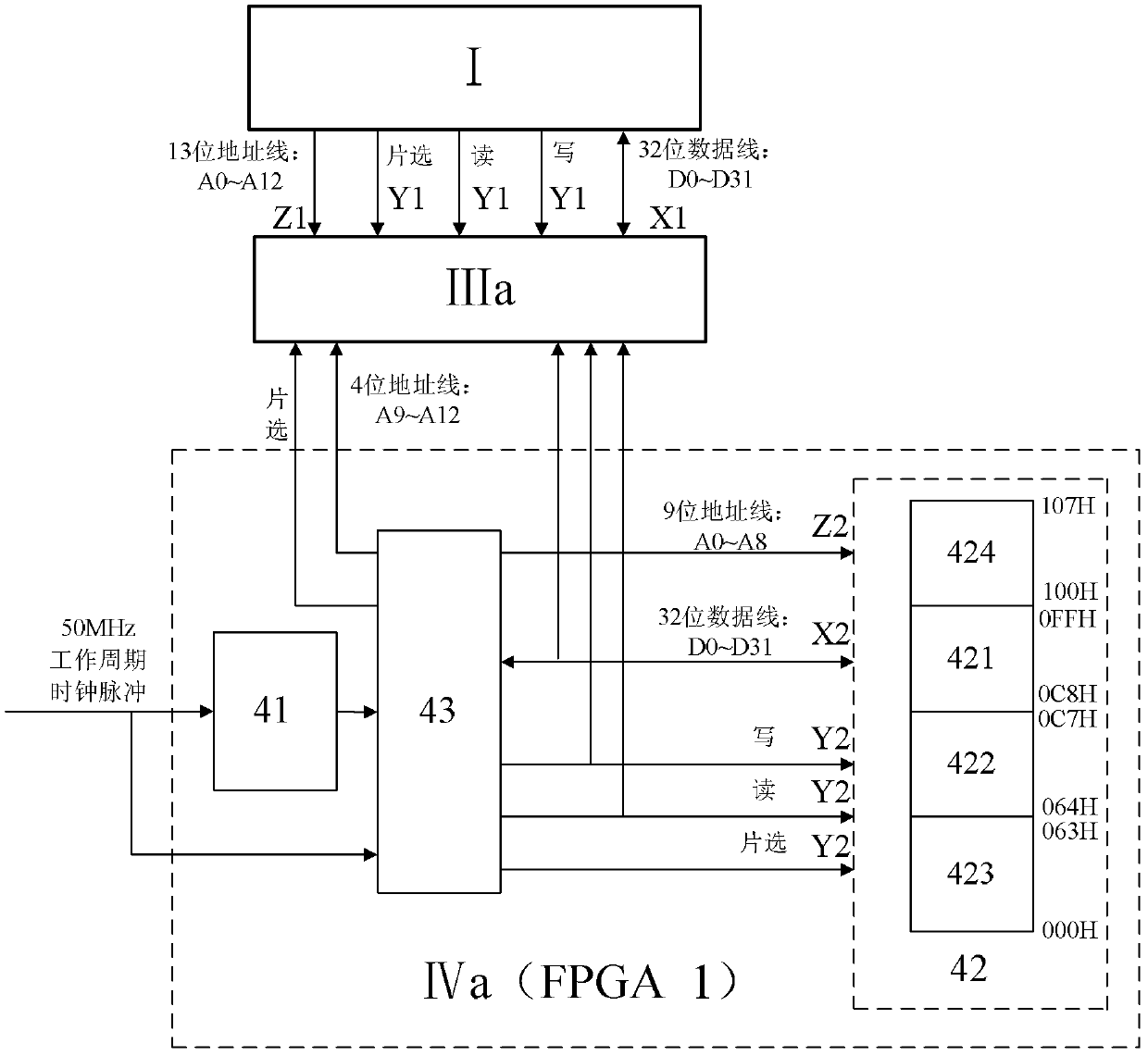

[0146] Such as figure 2 As shown, the ARM control module I includes an embedded ARM microprocessor 10, a human-computer interaction circuit 11, a control circuit 12, a reset circuit 13, and a JTAG debugging interface circuit 14, and the embedded ARM microprocessor 10 is used as the control core, respectively Connect with human-computer interacti...

Embodiment 2

[0160] A timer device composed of ARM+FPGA, its basic structure is the same as that of Embodiment 1, and also uses the embedded ARM microprocessor as the control module, FPGA as the timing processing module, including ARM control module I, memory module II, FPGA timing Module IV, dual-port RAM module III and power module V; ARM control module I is connected to memory module II and dual-port RAM module III respectively, FPGA timer module IV is connected to dual-port RAM module III, and power module V is ARM control Module Ⅰ, memory module Ⅱ, dual-port RAM module Ⅲ and FPGA timer module Ⅳ provide power supply; The difference between the present embodiment 2 and embodiment 1 is: in embodiment 1, dual-port RAM module Ⅲ and the timing timer composed of FPGA1 The device module IV is two independent modules; and in the present embodiment, the dual-port RAM module III is embedded in the FPGA2 forming the FPGA timer module IV, and FPGA2 is a block with the dual-port RAM module III and t...

Embodiment 3

[0162] The method for implementing the timer by using the timer device composed of the above-mentioned ARM+FPGA is to use the embedded ARM microprocessor in the ARM control module as the control core, to carry out timing control processing with the FPGA timer module, and to use the dual-port RAM module as the control core. The bridge for data transmission between the ARM control module and the FPGA timer module to realize data communication; during the initialization process of the embedded ARM microprocessor, clear each storage unit of the dual-port RAM and clear the timing unit in the FPGA ;

[0163] In the process of compiling the user program, the ARM control module transmits the timing parameters and usage status information set by each numbered timer used by the user program to the dual-port RAM module, and the ARM control module executes the timer of a certain numbered timer in the user program. When outputting, the running state information of the numbered timer is tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com