The preparation method of multi-layer pcb board

A PCB board and core board technology, applied in the field of multi-layer PCB board preparation, can solve the problems of increased production cost, high product defect rate, and difficulty in precise copper thickness, so as to save production cost, reduce scrap rate, and reduce copper accurately. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

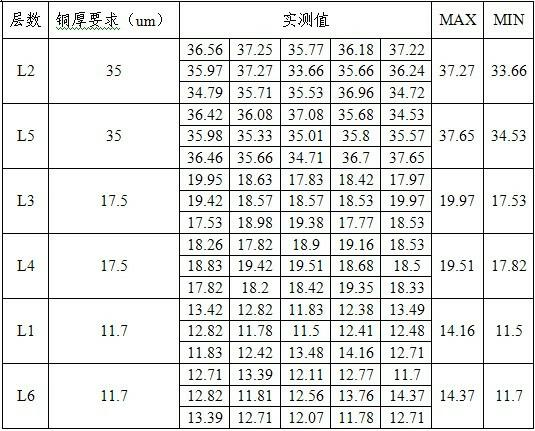

[0015] The preparation method of the multi-layer PCB board of the present invention will be further described in detail below by taking the manufacture of a six-layer PCB board as an example.

[0016] For the convenience of description, the outer layers of the six-layer PCB are marked as layers L1 and L6, and the middle layers are marked as layers L2, L3, L4, and L5. Among them, the target copper thickness of the inner layers L2 and L5 is 1OZ (ounce, 1oz=28.35 grams), and the target copper thickness of the L3 and L4 layers is 0.5OZ. The target copper thickness of the outer layers L1 and L6 is 1 / 3OZ.

[0017] The preparation method of this six-layer PCB board comprises:

[0018] step one:

[0019] Design and manufacture three double-sided core boards: the first core board, the second core board and the third core board. The upper and lower sides of the first core board are respectively used as the L1 layer and the L2 layer, the upper and lower sides of the second core board ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com