Stacked chip package structure and method

A chip packaging structure and chip packaging technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of large package structure, high cost, and inability to meet the development trend of miniaturization of electronic products, so as to reduce the volume of products Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

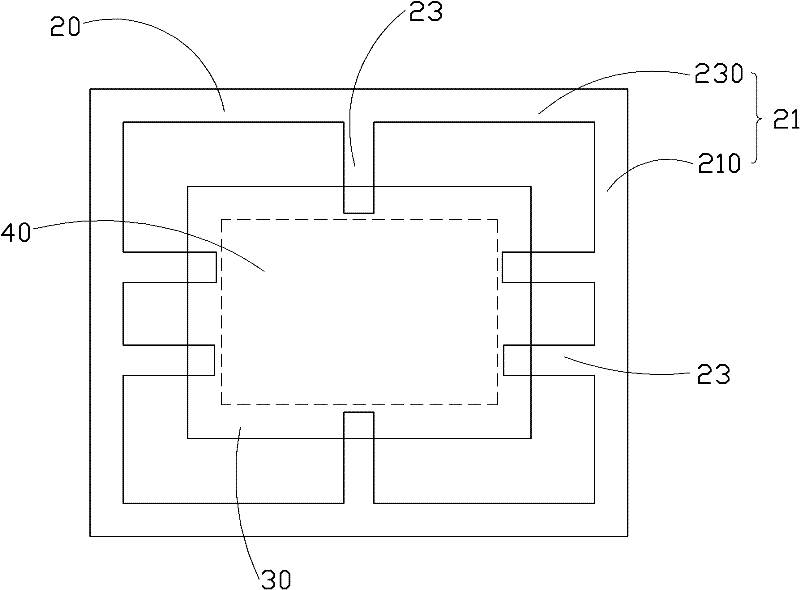

[0027] figure 1 It is a schematic cross-sectional view of the assembly of the stacked chip packaging structure 100 without the encapsulant 10 of the present invention. Please also refer to FIG. 3( e ), the stacked chip packaging structure 100 of the present invention includes an encapsulant 10 , a substrate 20 , a first chip 30 and a second chip 40 .

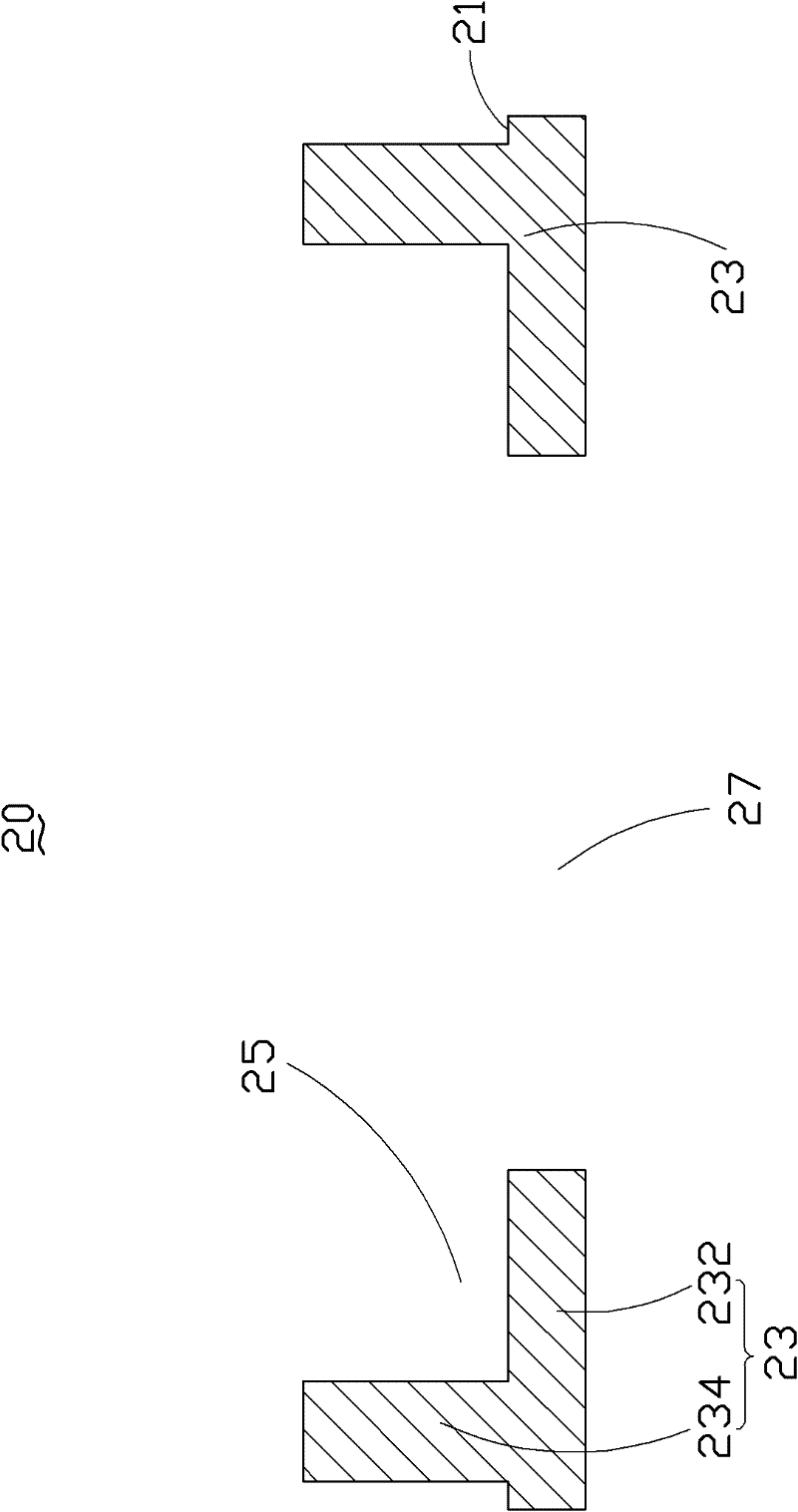

[0028] Please refer to figure 1 and figure 2 , the substrate 20 is a frame structure, which includes a body 21 , a plurality of pins 23 , a receiving portion 27 and a recessed portion 25 . The body 21 includes a pair of opposite first sidewalls 210 and a pair of opposite second sidewalls 230 , and the first sidewalls 210 and the second sidewalls 230 are respectively connected vertically.

[0029] The pins 23 are independent from each other and connected to the body 21 respectively. In this embodiment, there are six pins 23 . Wherein, the inner wall of each first side wall 210 is respectively connected with a pair of pins 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com