Low drop-out voltage regulator with wide bandwidth power supply rejection ratio

A voltage regulator, low dropout technology, applied in the field of integrated circuits, can solve problems such as damage to the performance of analog circuit blocks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any embodiment or design described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments or designs.

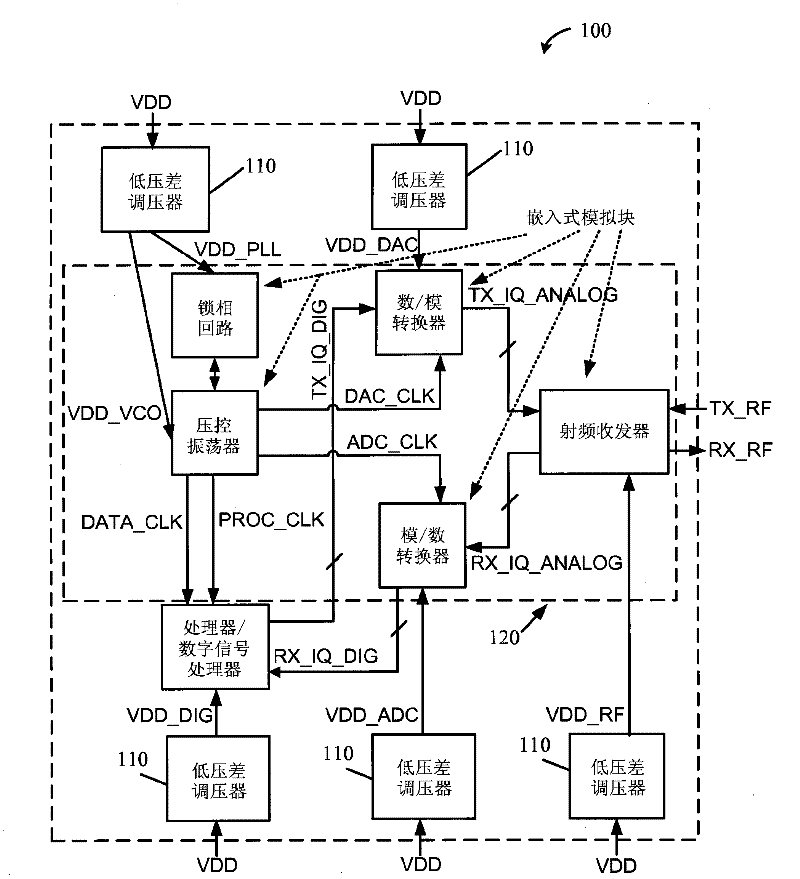

[0025] Wide bandwidth Power Supply Rejection Ratio (PSRR) Low Dropout (LDO) voltage regulators are noise-sensitive individual analog circuits such as Phase-Locked Loops (PLLs), Voltage-Controlled Oscillators (VCOs), high-speed Digital-to-Analog Converters (DACs) ), reference current generators for high-speed analog-to-digital converters (ADCs), and other wide-bandwidth analog cores) to generate clean voltage supplies. Use of individual wide-bandwidth PSRR LDO regulators for separate analog blocks in the SoC allows on-package supply pumps to be shared between multiple PLLs and other embedded analog cores; thereby reducing the need for on-package supply pumps for noise-sensitive analog circuits Number of.

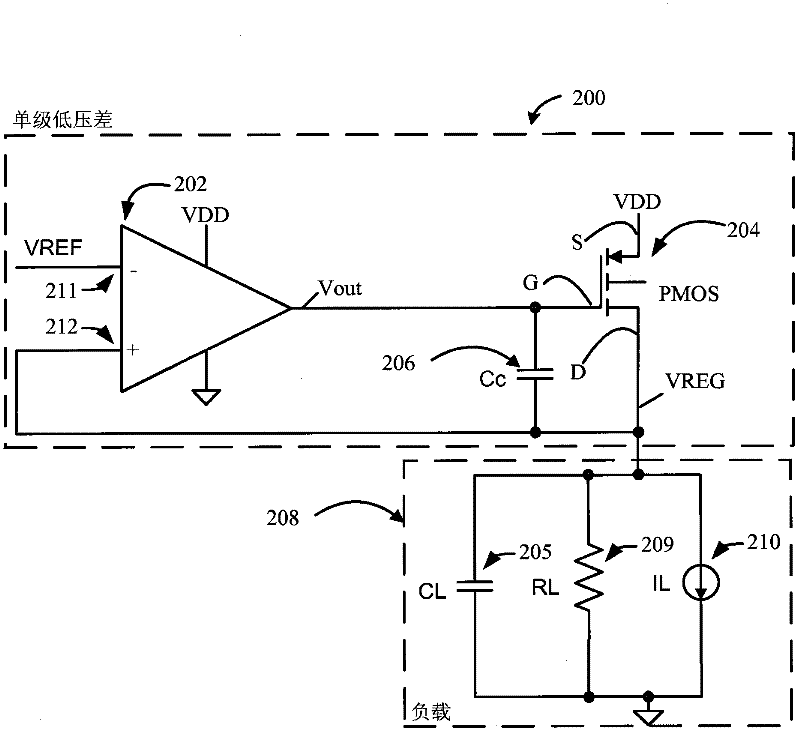

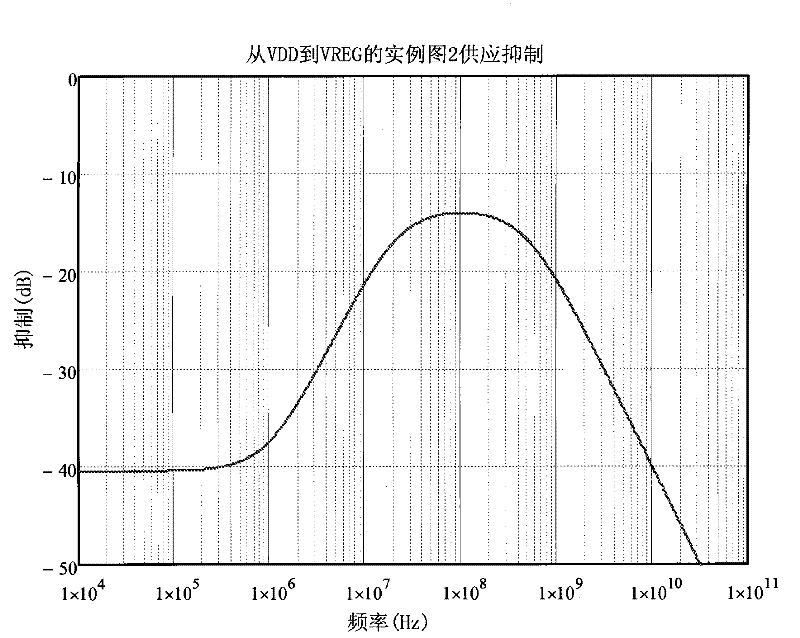

[0026] Figu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com