Advanced synthesizing method for integrated circuit

A technology of integrated circuits and comprehensive methods, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of difficult expansion of execution efficiency and flexibility, and achieve the effect of high execution efficiency and high enforceability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings.

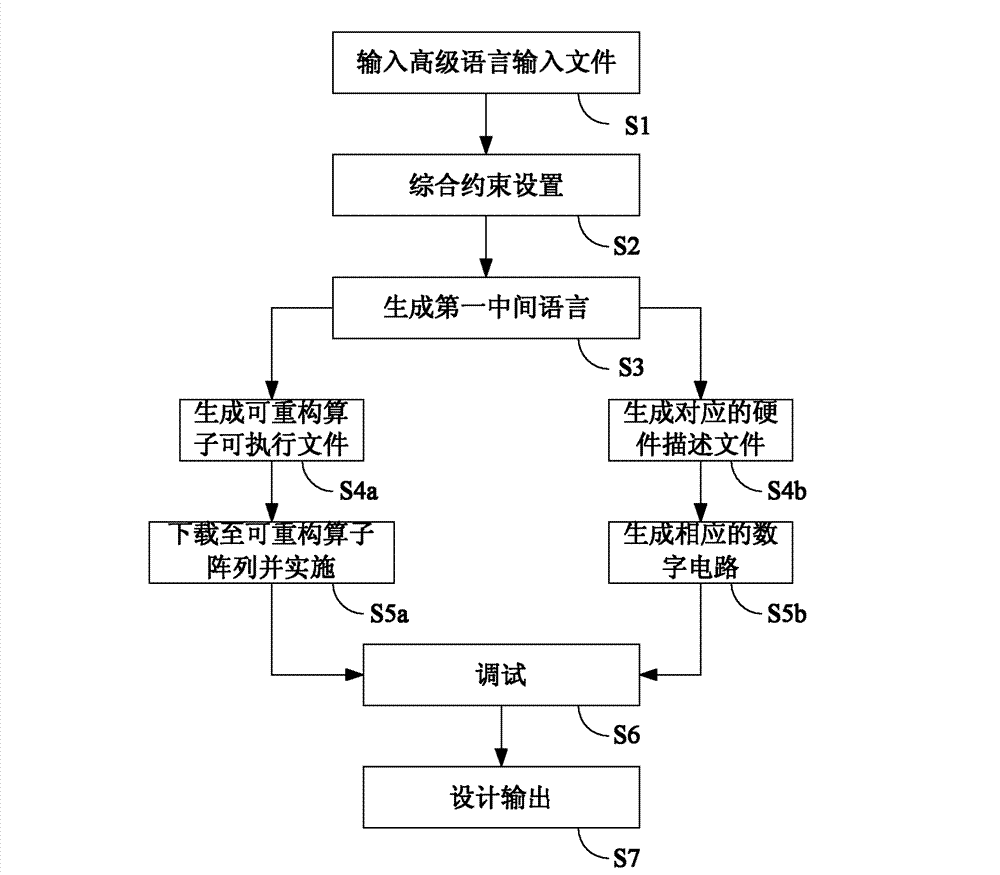

[0062] Please refer to figure 2 , the high-level synthesis method of the integrated circuit of the present embodiment, comprising steps:

[0063] S1, input a high-level language input file describing a digital circuit.

[0064] The high-level language input file in this embodiment is an input file describing the situation of the digital circuit, which can be C language or other high-level languages, such as Java, C++, Matlab, etc.

[0065] S2, performing comprehensive constraint setting.

[0066] The comprehensive constraint in this embodiment is realized by man-machine interface such as file input or keyboard input.

[0067] In this embodiment, the calculation speed, power consumption, actual circuit area used, relative ratio of various circuit resources, hardware structure of the target reconfigurable operator array, input f...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap