Formation method for grid structure

A technology of gate structure and graphics, which is applied in the direction of semiconductor devices, etc., can solve the problem of low reliability of gate structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

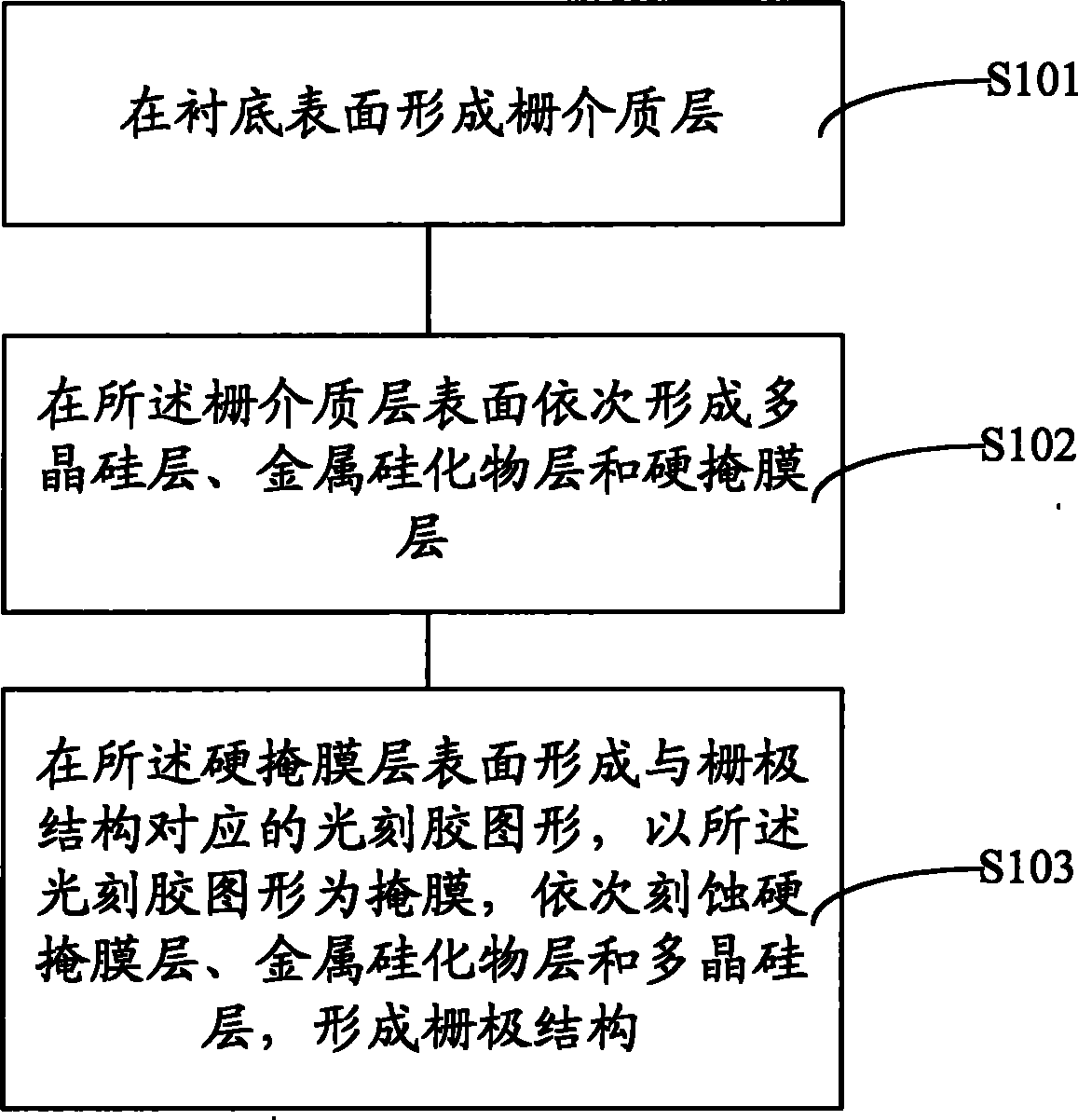

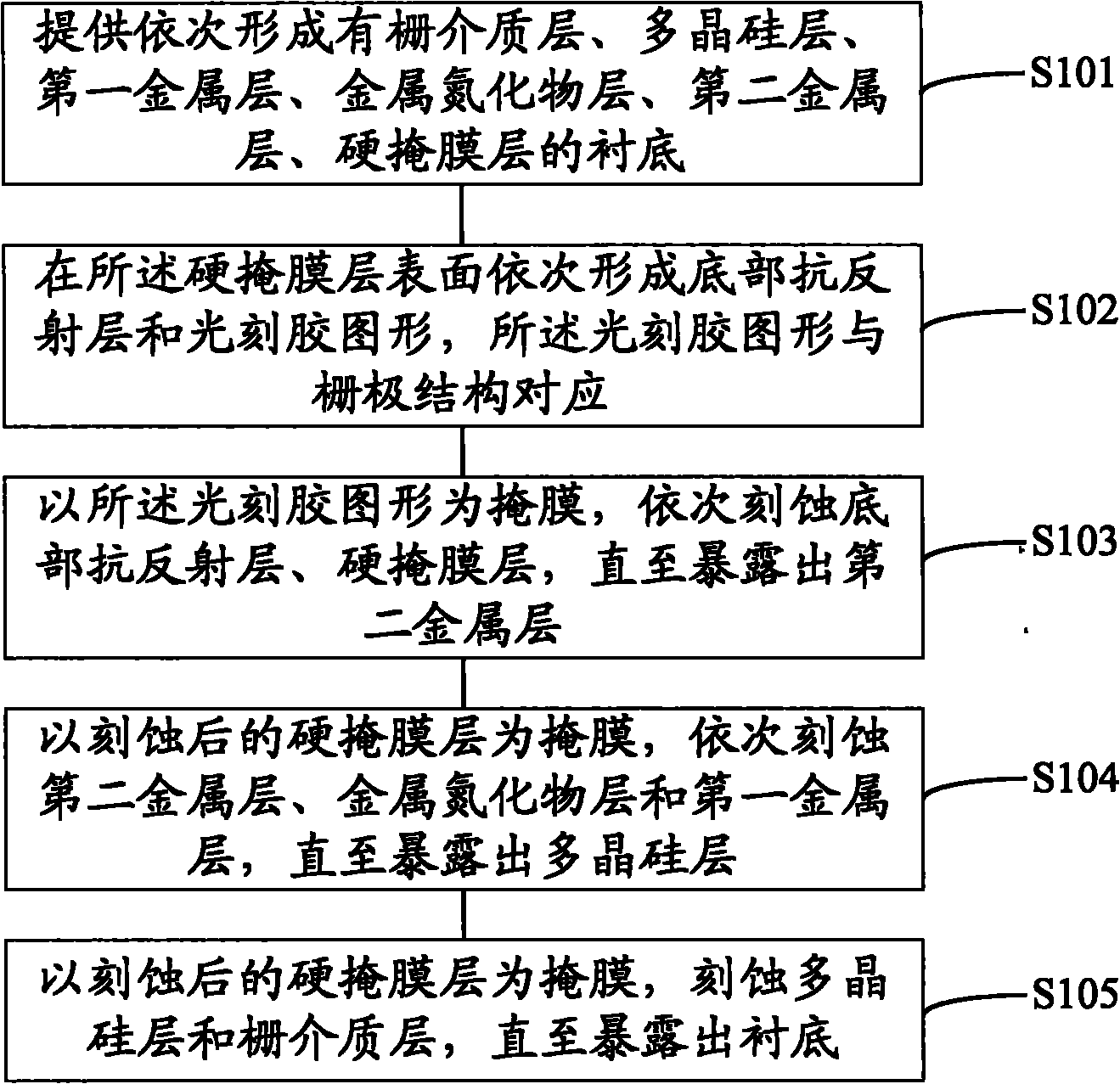

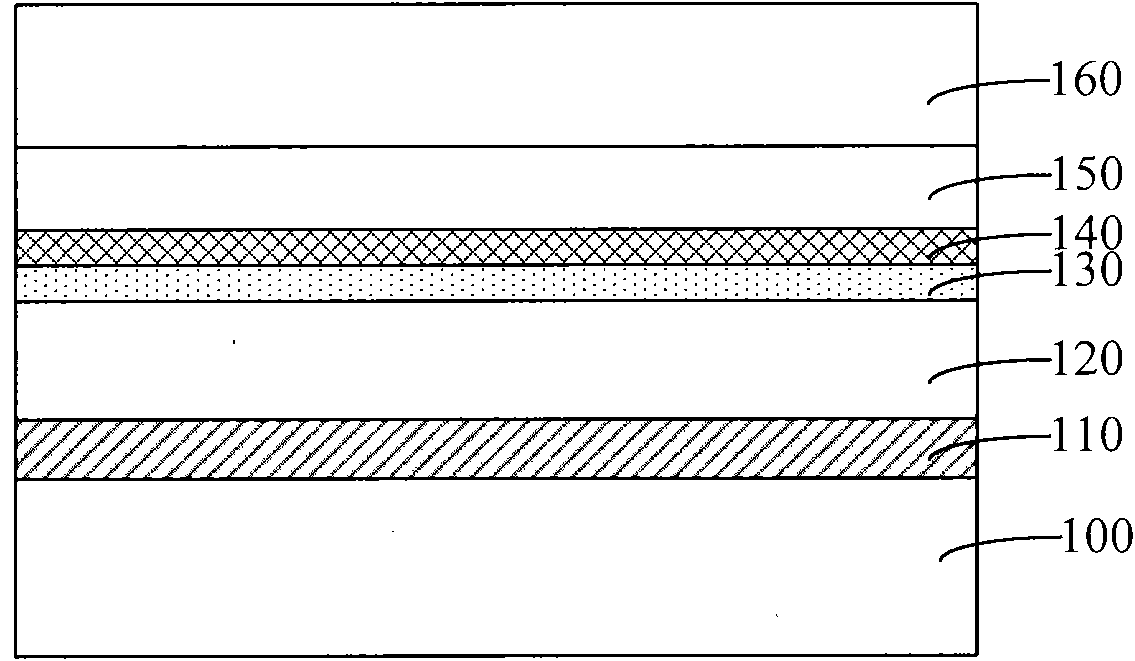

Method used

Image

Examples

Embodiment Construction

[0018] The existing gate structure formation process will use plasma etching, the plasma etching is too strong, the etching metal silicide layer will cause damage to the polysilicon layer, and finally form etch pits (Pits) on the surface of the gate dielectric layer, resulting in gate The electrode structure fails; while the weak plasma etching will form some impurities in the polysilicon layer, and finally form the residual impurities on the surface of the dielectric layer, which will degrade the performance of the gate structure. Aiming at the defects formed in the formation process of the above-mentioned gate structure, those skilled in the art usually optimize by adjusting parameters such as etching power and etching time, but due to the presence of CF 4 It is difficult to optimize the plasma etching by the above optimization method. If the etching power is high or the etching time is long, etch pits will be formed, and if the etching power is small or the etching time is s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com