Nonvolatile memory and arrangement thereof

A non-volatile, memory technology, applied in the field of non-volatile memory layout, can solve the problems of complex process, high cost, poor component yield, etc., to improve component performance, increase component density, and reduce leakage current Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

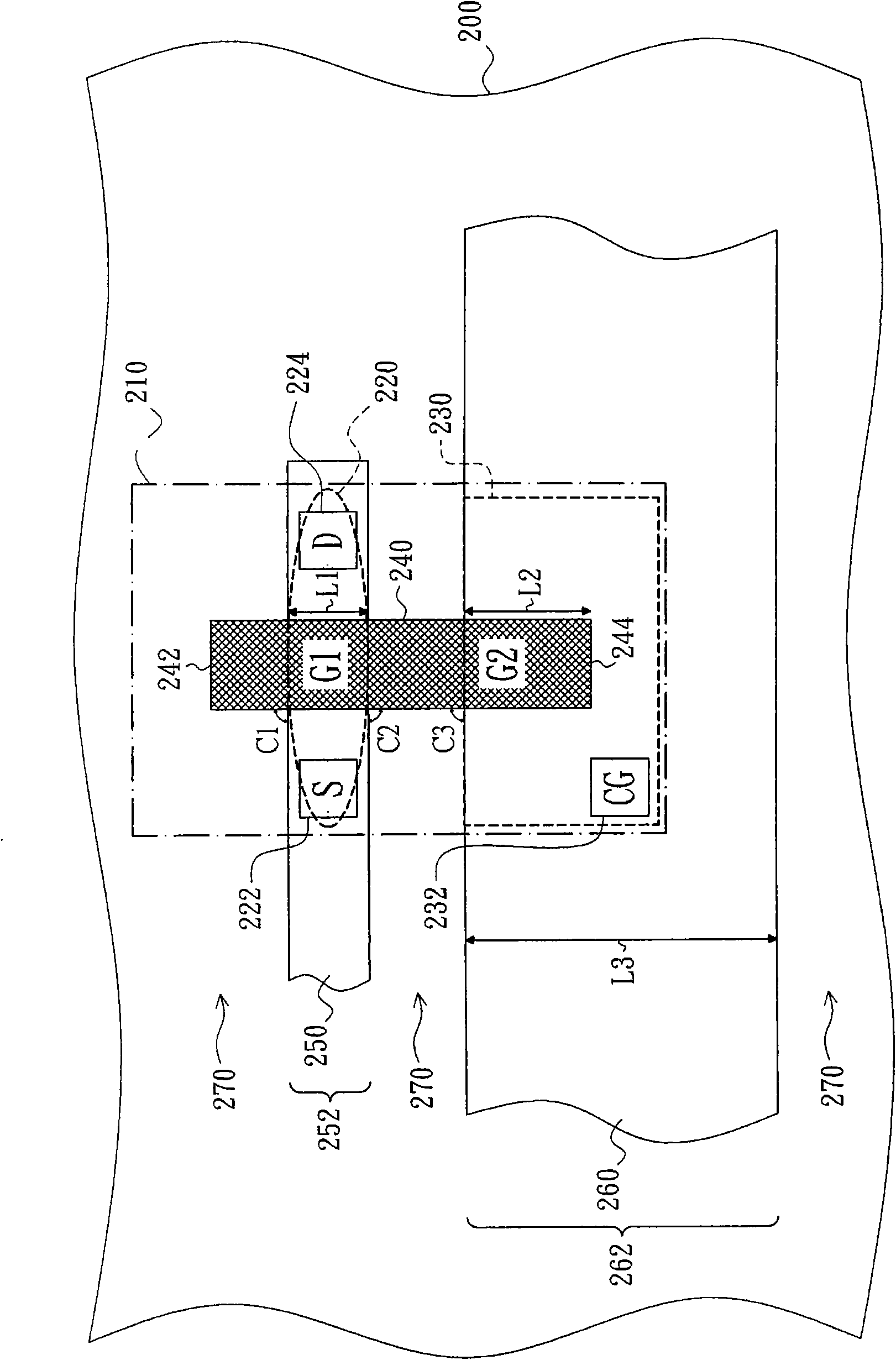

[0056] figure 2 It is a schematic top view of a non-volatile memory unit according to an embodiment of the present invention.

[0057] Please refer to figure 2 , the non-volatile memory unit 210 of the present invention is composed of a semiconductor substrate 200, a conductor 240, a plurality of isolation structures 270, a first-type doped well 260, two first ion-doped regions 222, 224 and a second ion-doped impurity region 232.

[0058] A plurality of isolation structures 270 parallel to each other are disposed in the semiconductor substrate 200 , such as shallow trench isolation structures (Shallow Trench Isolation, STI). These isolation structures 270 partition the semiconductor substrate 200 into transistor regions 252 and capacitor regions 262 parallel to each other. The first-type doped well 260 is disposed in the container region 262 and is, for example, an N-type doped well.

[0059] In this embodiment, the semiconductor substrate 200 is, for example, an undoped...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com