Failure analysis method of gate oxide

A gate oxide layer and failure analysis technology, which is applied in the field of semiconductor manufacturing, can solve the problems of complex detection process, failure detection results, long detection cycle, etc., and achieve the effects of improving success rate, saving time, and easy control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

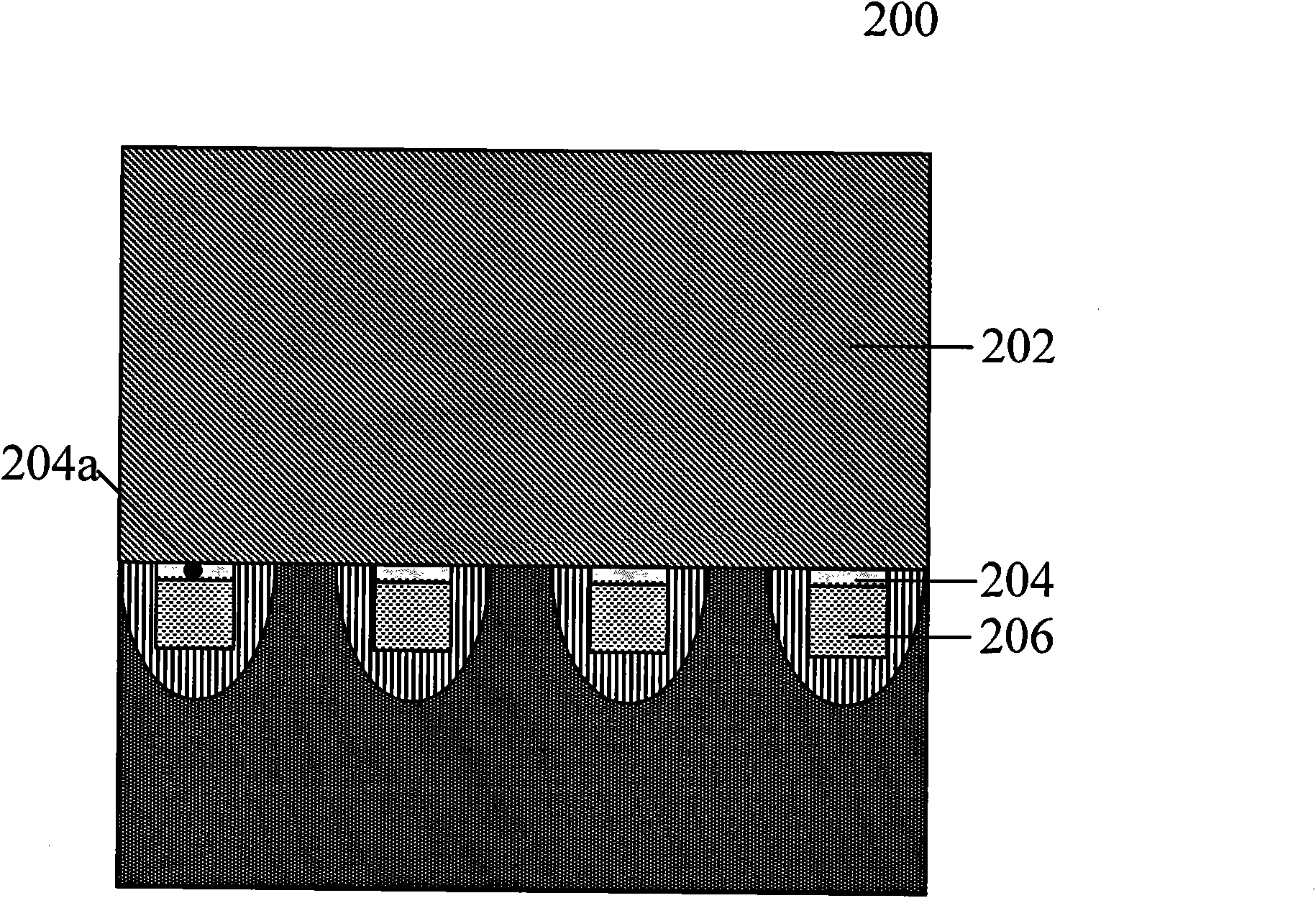

[0036] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0037] The method for performing failure analysis on the gate oxide layer in this embodiment includes:

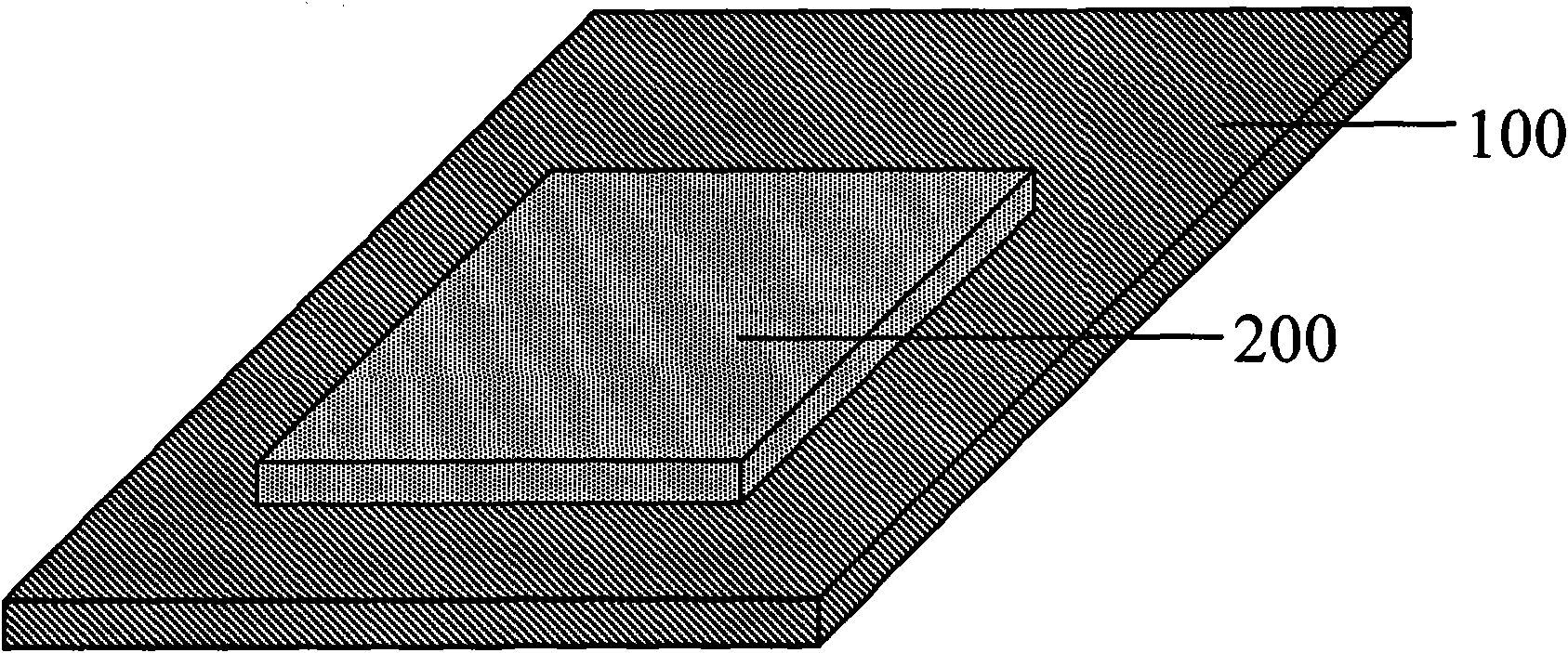

[0038] First, the invalid wafer is pasted upside down on the substrate with thermal gel, and the invalid wafer includes the substrate and the gate oxide layer on the substrate;

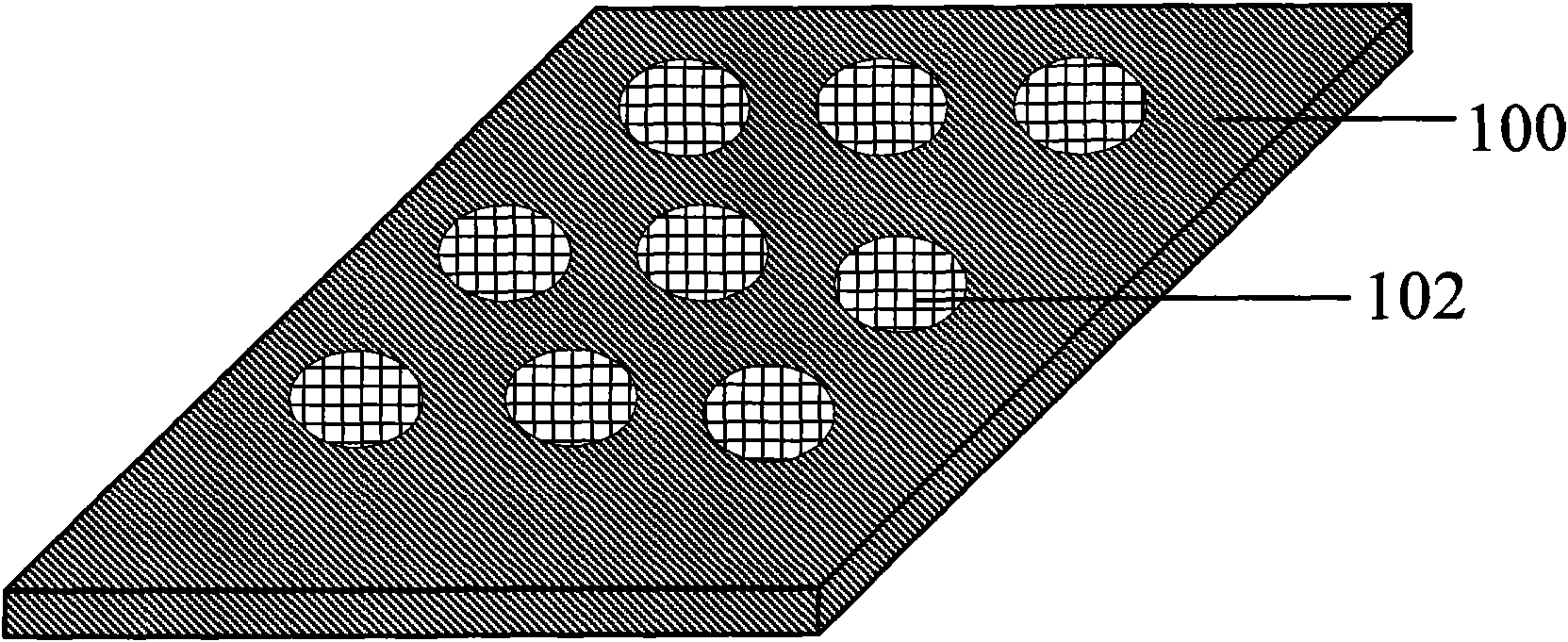

[0039] Preferably, in order to make the thermal gel evenly coated and to have good adhesion between the failed wafer and the substrate, the thermal gel is divided into a plurality of uniform thermal gel points, which are evenly dropped on the substrate in an array;

[0040] Preferably, the invalid wafer is pasted upside down on the substrate with thermal gel, further comprising: applying uniform pressure to the substrate and the wafer and heating it, so that the two ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com