Passivation layer and its manufacturing method

A manufacturing method and passivation layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of reducing the yield rate of semiconductor chips, poor adhesion, falling off, etc., to avoid peeling and Effects of cavitation, promotion of low temperature formation, and slowing down of migration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with accompanying drawing, the present invention is described in further detail:

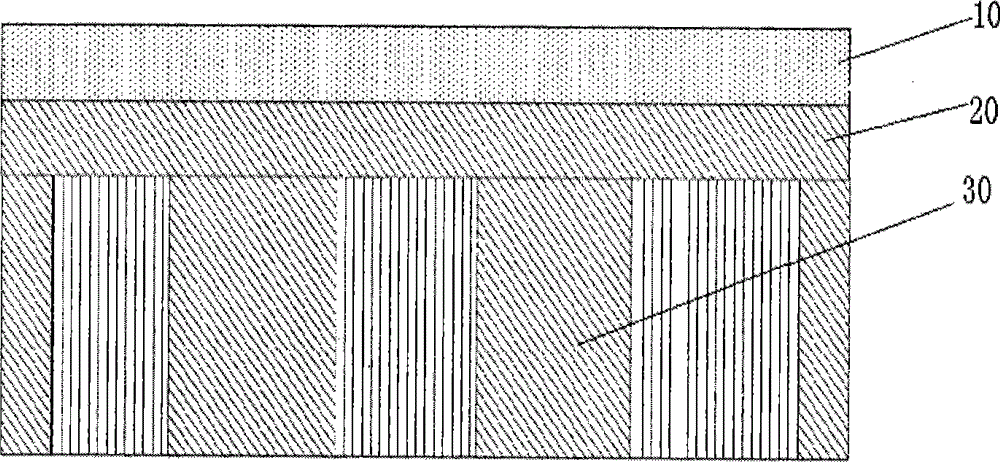

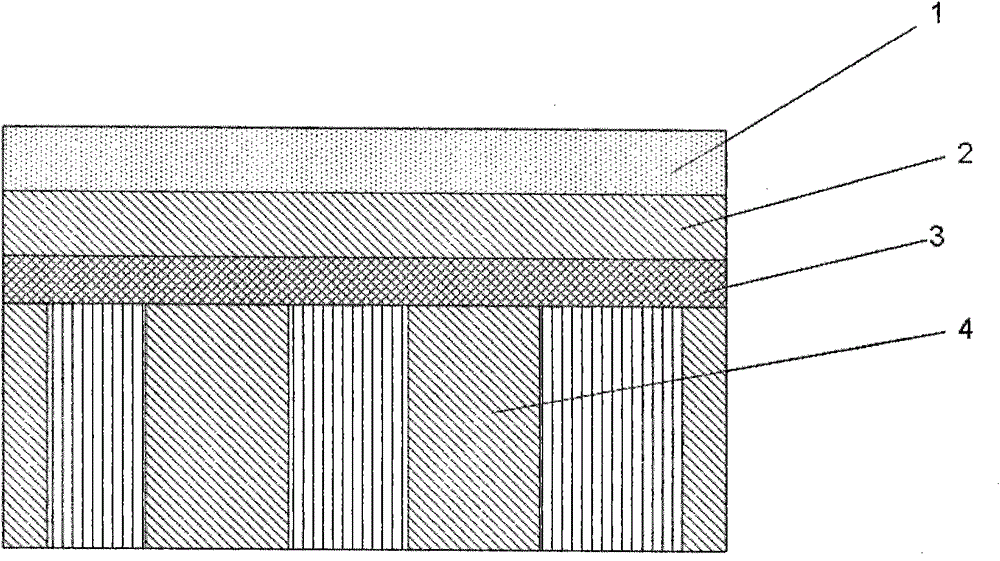

[0024] figure 2 In , the device layer of the semiconductor chip substrate is omitted, and the structure of the metal line and the passivation layer is only drawn schematically. Those skilled in the art can understand that a CMOS device can be pre-fabricated in the semiconductor substrate, and a metal line can be formed by using a dual embedded interconnection process.

[0025] Such as figure 2 As shown, the passivation layer of the present invention includes an amorphous silicon layer 3 formed on the semiconductor substrate and covering the metal line 4 in the semiconductor substrate, and formed sequentially on the amorphous silicon layer 3 Silicon dioxide layer 2 and silicon nitride layer 1. The metal wire 4 is copper wire. That is to say, the metal wire 4 of the semiconductor chip is made by copper wire technology.

[0026] The thickness of the amorphous sili...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com