Multiple-rate, quasi-cycling and low density decoder for parity check codes

A low-density parity, quasi-loop technology, applied in the field of decoder structure, can solve the problems of log-BP algorithm hardware implementation difficulties, waste of resources, and large footprint.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

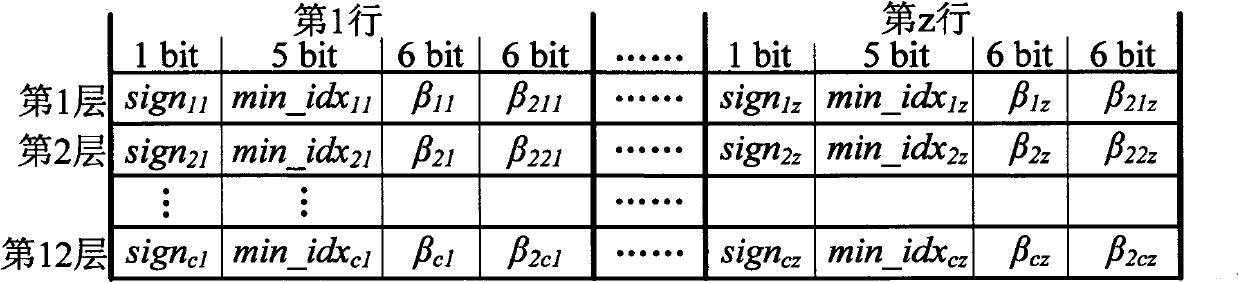

[0035] Each column of the check matrix of the quasi-cyclic low-density parity-check code corresponds to a variable node, and each row of the check matrix corresponds to a check node. The check matrix is composed of M×N sub-matrices, and each sub-matrix is z×z The elementary matrix obtained by the cyclic shift of the zero matrix or the identity matrix of z×z, where the size of M and N is stipulated by IEEE 802.16e, M=12, 8, 6, 4, N=24, and the size of the sub-matrix is also As stipulated by IEEE 802.16e, there are 19 sizes, z=24, 28, 32, . . . , 96.

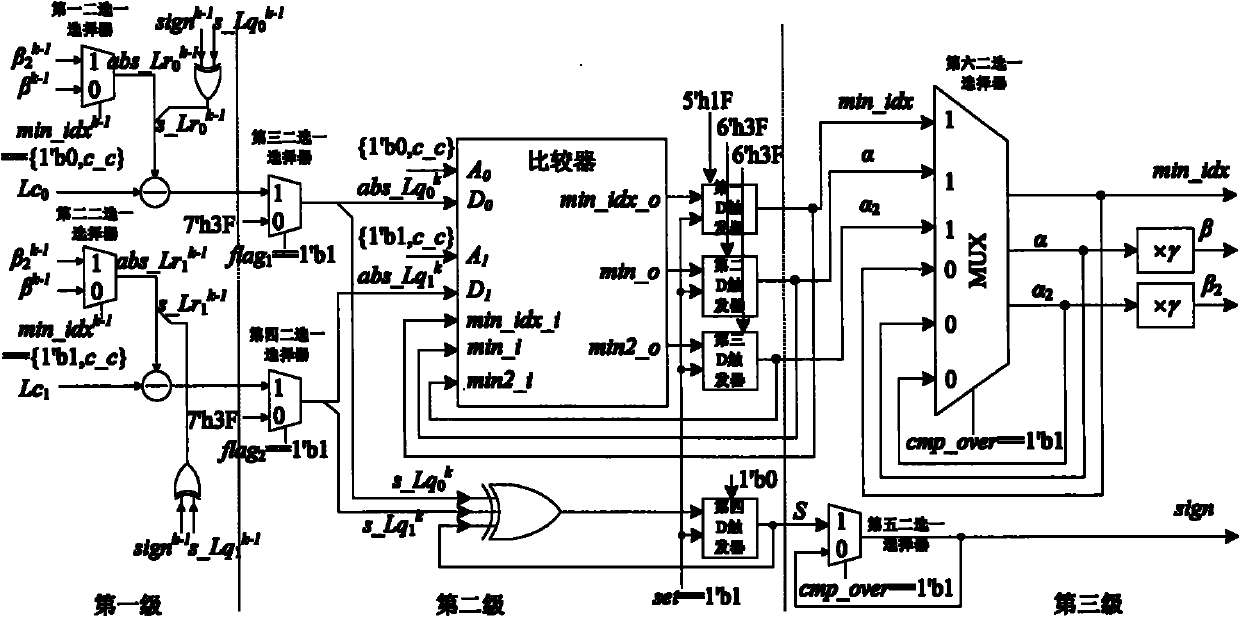

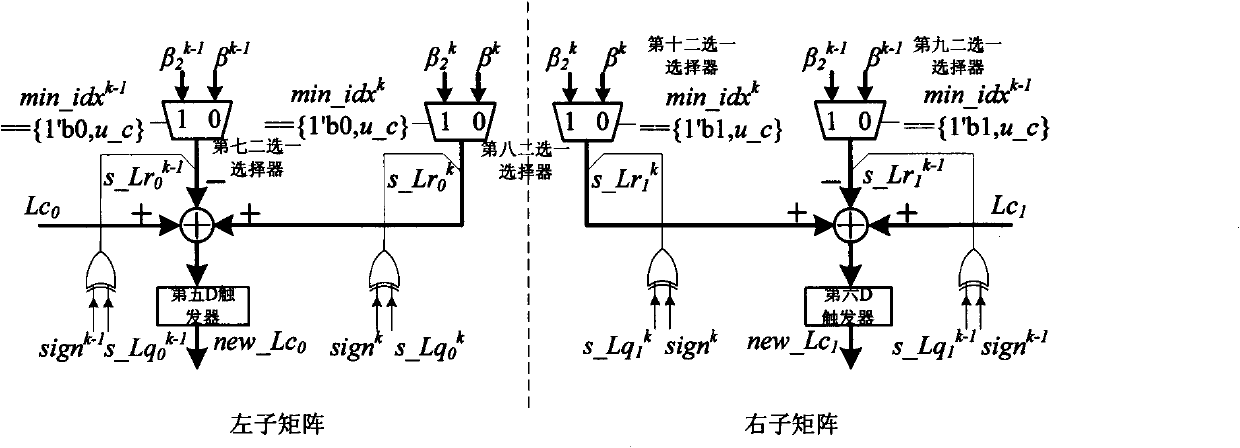

[0036] The present invention proposes a multi-code-rate quasi-cyclic low-density parity-check code decoder on the basis of studying the check matrix, and its structural block diagram is as follows figure 1 As shown, the decoder includes variable node information storage group 1, check matri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com