Double-phase-locked loop circuit and control method thereof

A dual phase-locked loop and control method technology, applied in the field of phase-locked loops, can solve the problems of inability to track temperature or process, increase the complexity of circuit design, and small adjustable frequency range, so as to expand the frequency adjustment range and reduce design complexity. degree, to achieve the effect of on-chip integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

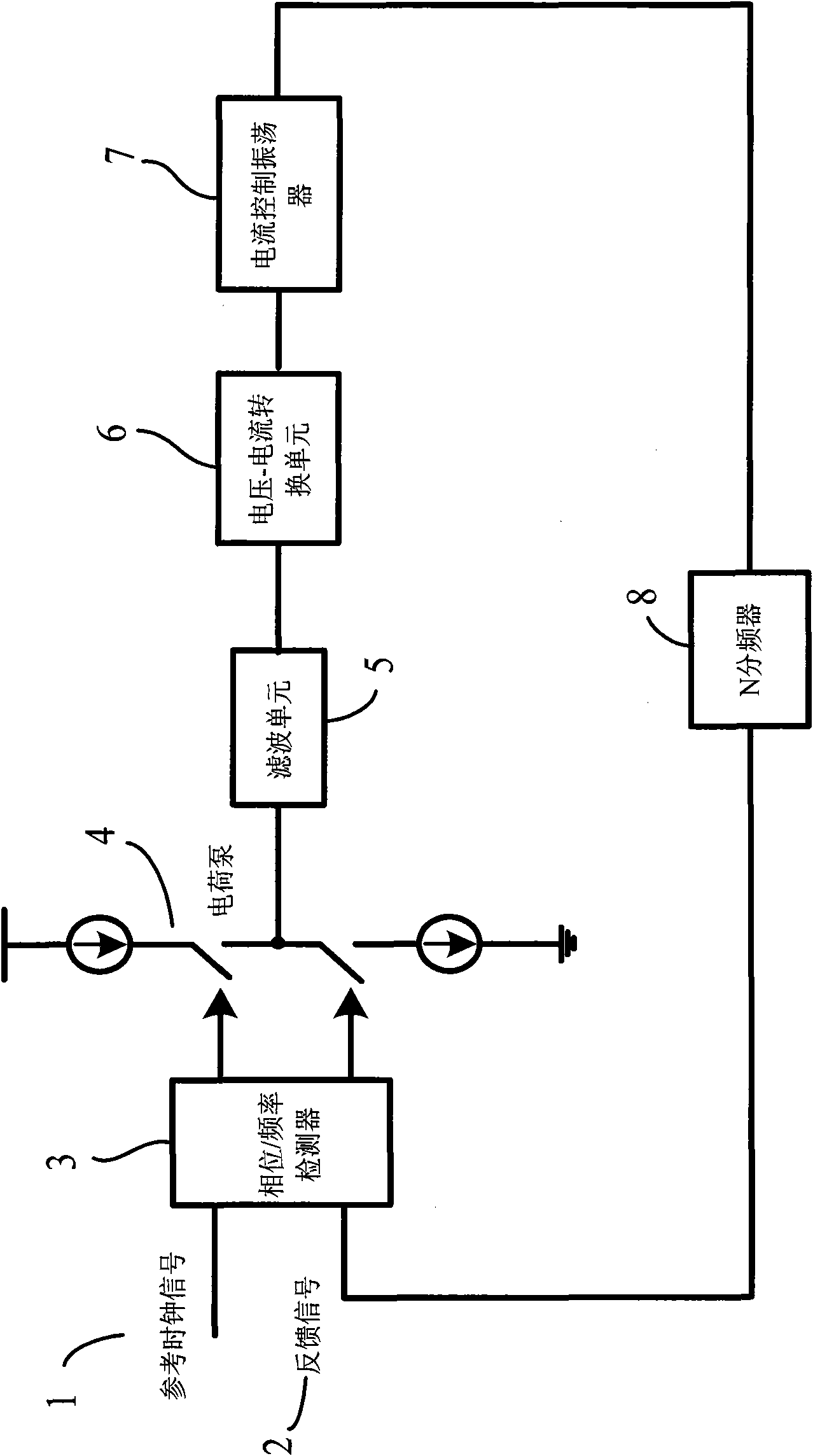

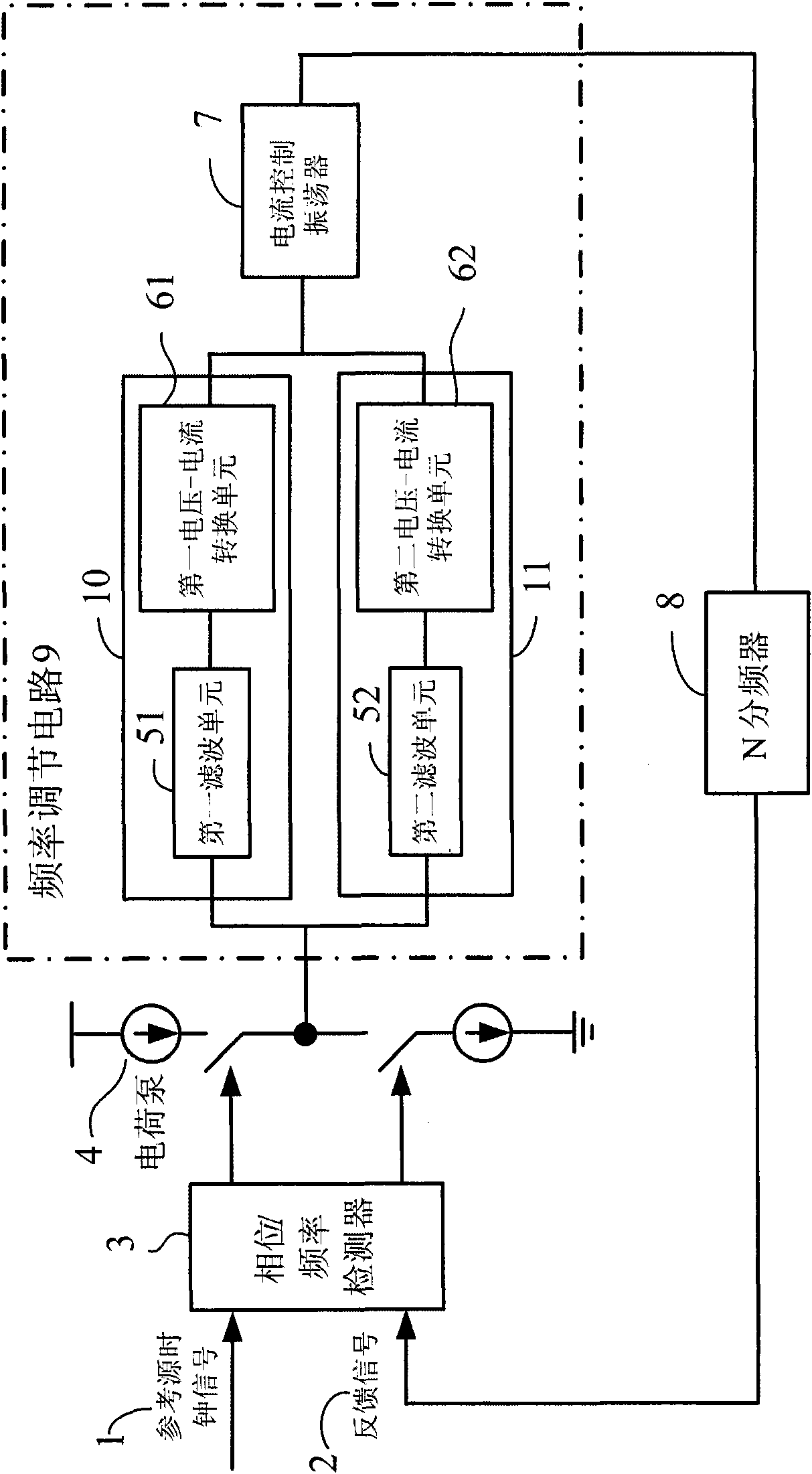

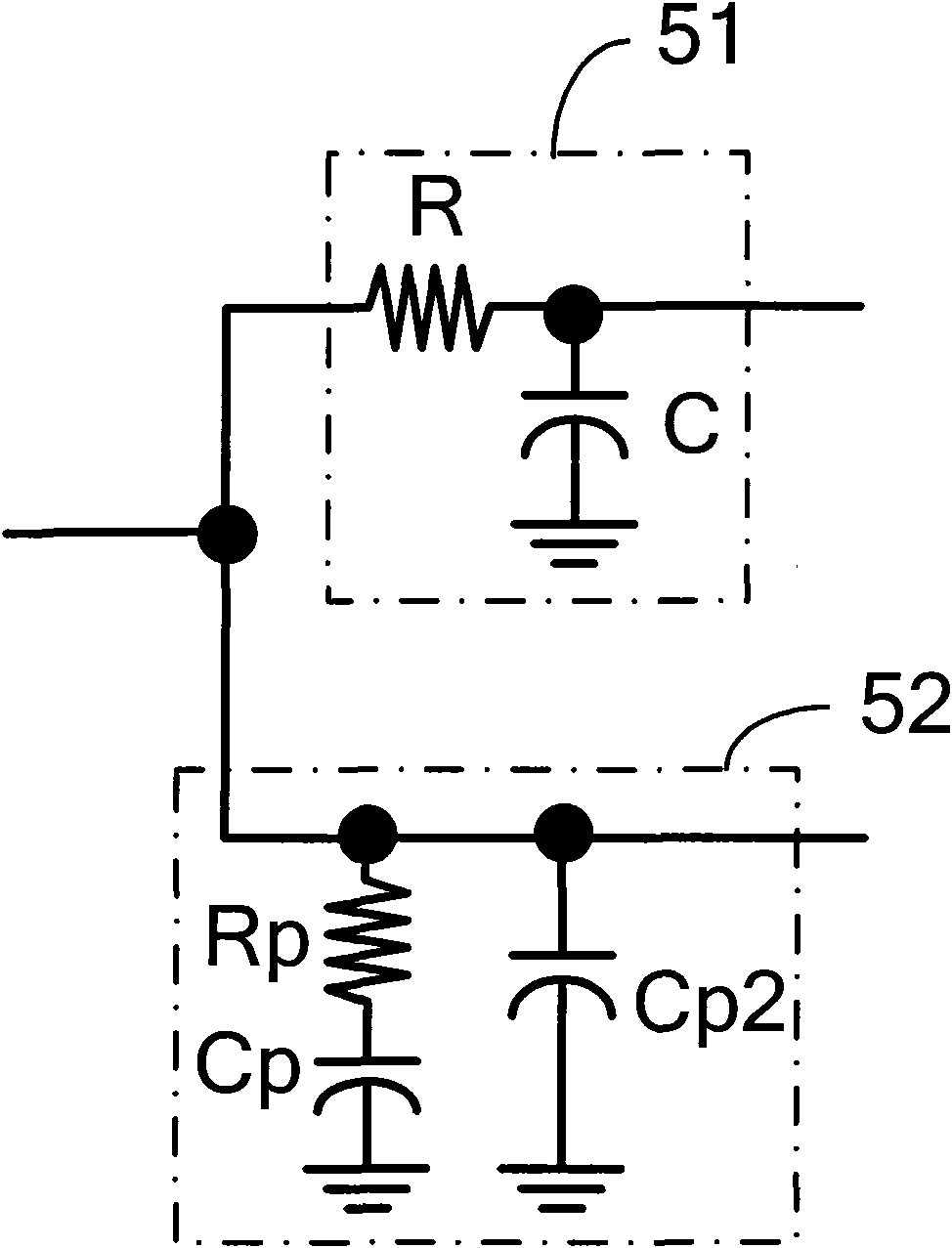

[0034] figure 2 This is a schematic diagram of the first specific embodiment of the dual phase-locked loop circuit of the present invention, and the dual phase-locked loop in the present invention refers to, but is not limited to, a high-frequency narrow-band phase-locked loop. like figure 2 As shown, in this embodiment, the dual phase-locked loop circuit includes a phase / frequency detector 3, a charge pump 4, a frequency adjustment circuit 9, an N frequency divider 8, and a reference clock coupled in sequence. Signal 1 is input to an input of the phase / frequency detector 3 . The output signal of the other end of the frequency adjustment circuit 9 generates a feedback signal 2 through the N frequency divider 8 and is input to the other input end of the phase / frequency detector 3 . The frequency adjustment circuit 9 includes a coarse adjustment circuit 10 , a fine adjustment circuit 11 and a current controlled oscillator 7 . The coarse adjustment circuit 10 is connected in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com