Time-setting clock system of merging unit for realizing clock switching

A clock switching and clock system technology, applied in time division multiplexing system, transmission system, digital transmission system, etc., can solve problems such as large uncertainty, large delay and jitter of communication stack, and influence of synchronization accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

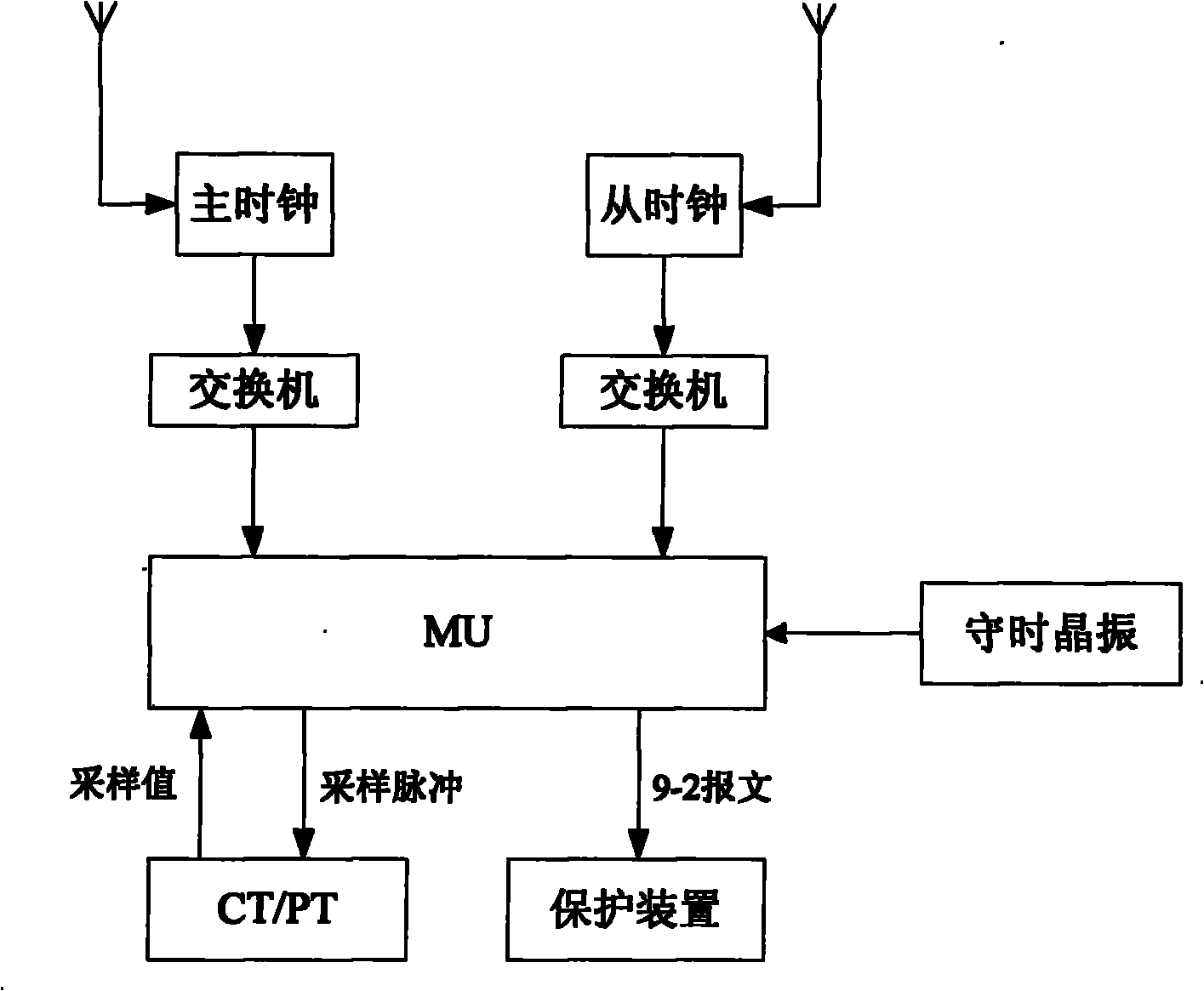

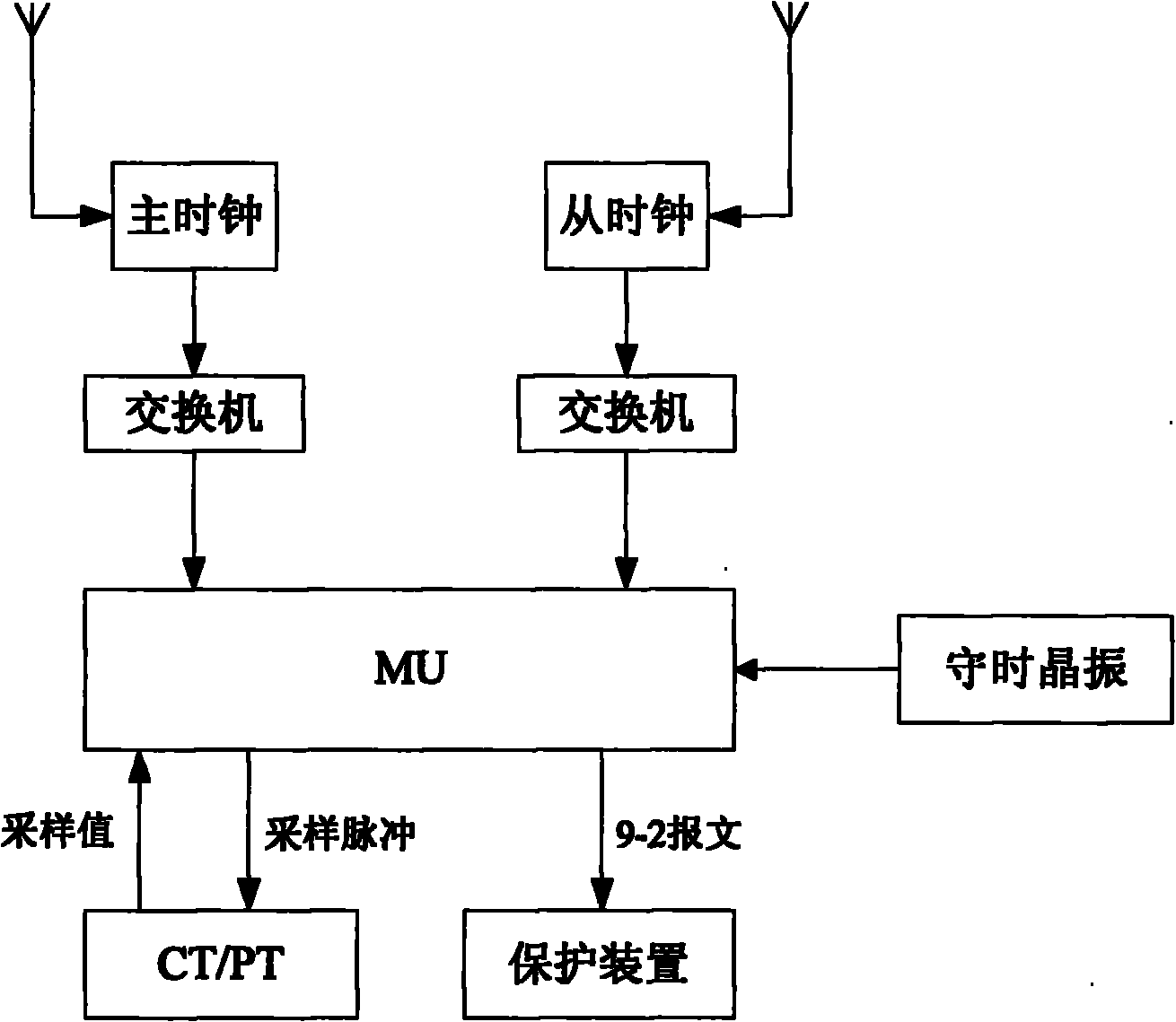

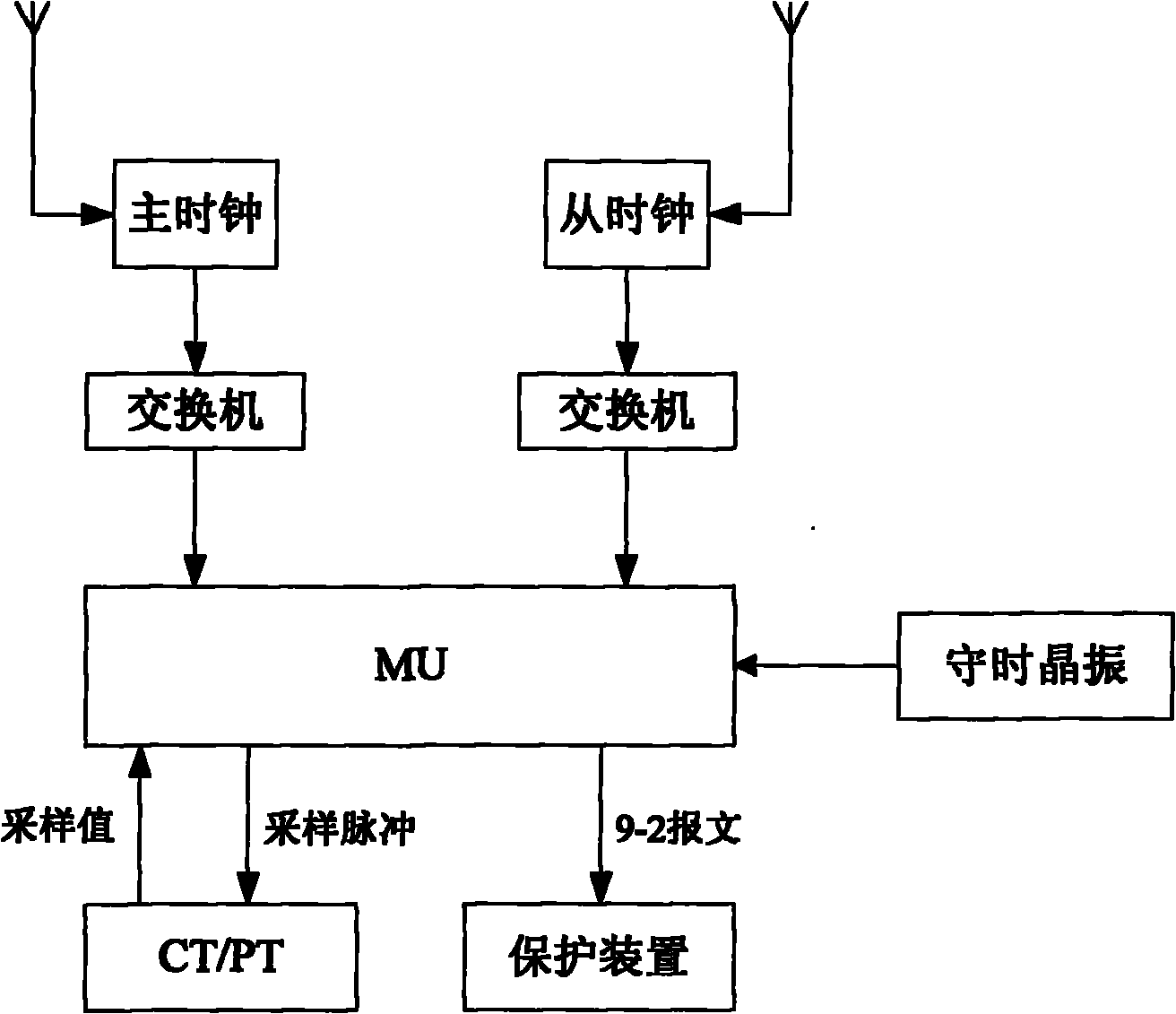

[0030] The present invention will be described in detail below in conjunction with the accompanying drawings.

[0031] Implementation of IEC61588 functions

[0032] PowerPC has the function of time stamping at the MAC layer in hardware. It is characterized by a 64-bit free-running timer from an external crystal oscillator or an internal clock, programmable clock source selection, and three cycle phases aligned with 1588 timers. The programmable timer outputs pulses, supports timestamps with nanosecond precision, and outputs second pulses.

[0033] Implementation of BMC algorithm

[0034] The BMC algorithm is the core algorithm of the IEC61588 system. In IEC61588, the port state of each clock is divided into nine states, including initialization state (PTP_INITIALIZING), master clock state (PTP_MASTER), slave clock state (PTP_SLAVE), and passive state (PTP_PASSIVE). The purpose of the BMC algorithm is to The status of each clock port is calculated to establish the best maste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com