Method for manufacturing solder lug

A fabrication method and technology for solder bumps, which are applied in the manufacture of semiconductor/solid-state devices, electrical components, and electrical solid-state devices, etc., can solve the problems of poor consistency of height and volume of solder bumps, abnormal shape of bumps, etc. The consistency of volume is easy to control and the effect of improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

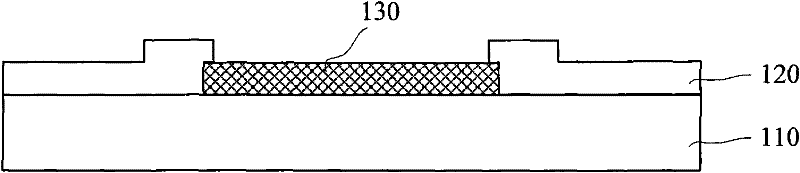

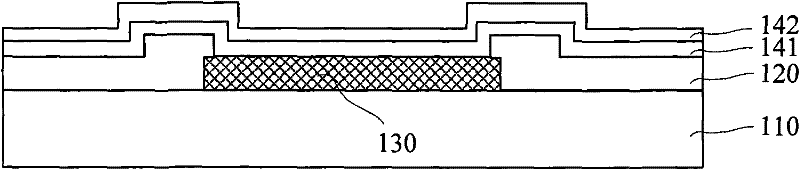

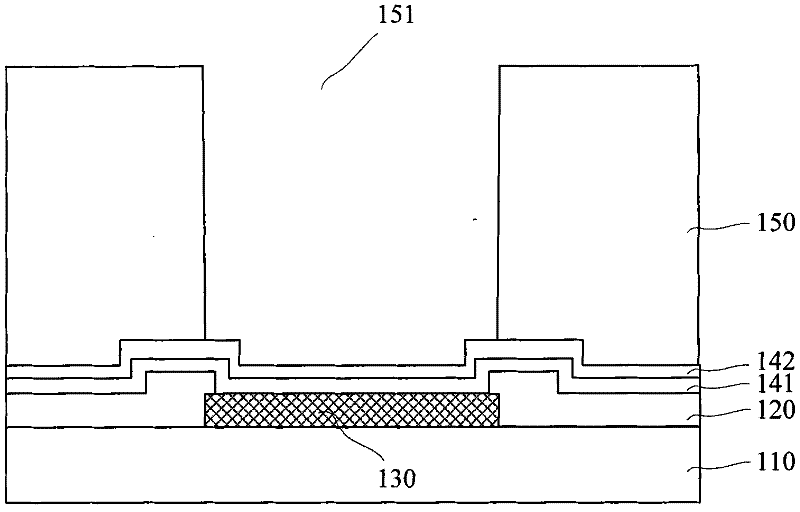

[0030] In order to make the purpose and features of the present invention more comprehensible, the specific implementation manners of the present invention will be further described below in conjunction with the accompanying drawings. It should be noted that the drawings are all in a very simplified form and use imprecise ratios, which are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0031] It will also be understood that when a layer is referred to as being "on" another layer or substrate, it can be directly on the other layer or substrate, or intervening layers may also be present. It will also be understood that when a layer is referred to as being "under" another layer, it can be directly under, and there may be one or more intervening layers. In addition, it will also be understood that when a layer is referred to as being "between" two layers, it can be the only layer between the two layers, or one or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com