Method for promoting chip finished product rate through increasing standard cell through hole

A standard unit and yield technology, applied in electrical components, special data processing applications, instruments, etc., can solve problems affecting chip yield, open circuit defects, affecting chip functions, etc., to improve layout search efficiency, reduce defect probability, The effect of improving the yield rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

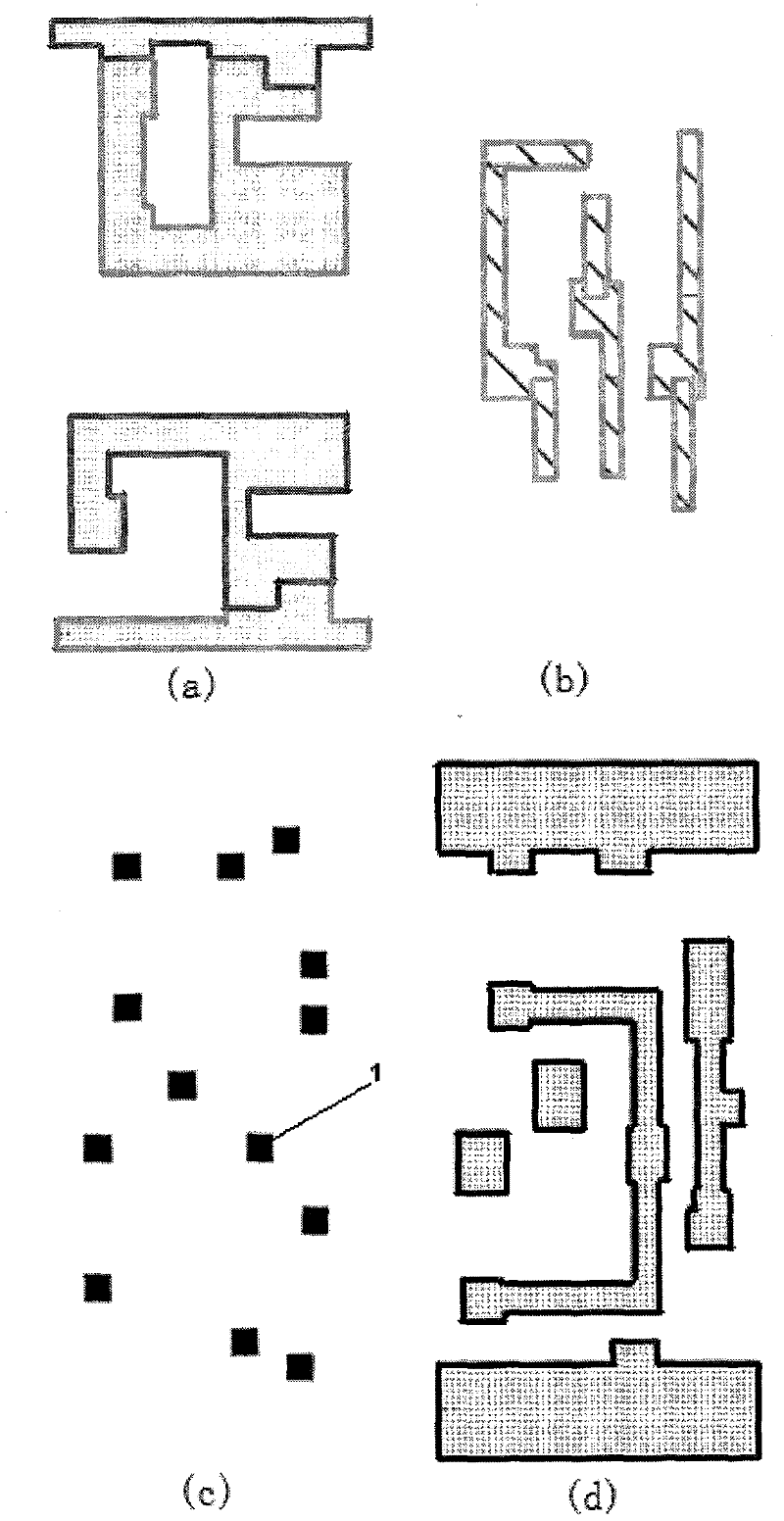

[0026] The present invention will be described below by taking the standard unit two-input AND gate as an example. The layout of the two-input AND gate is as follows figure 1 As shown, (a) is the layout of the active region (Active), (b) is the layout of the polysilicon layer (Poly), (c) is the layout of the contact layer, (d) is the layout of the metal layer . In this example, the via hole increase process starts with figure 1 The through hole marked with "1" in (c) is taken as an example.

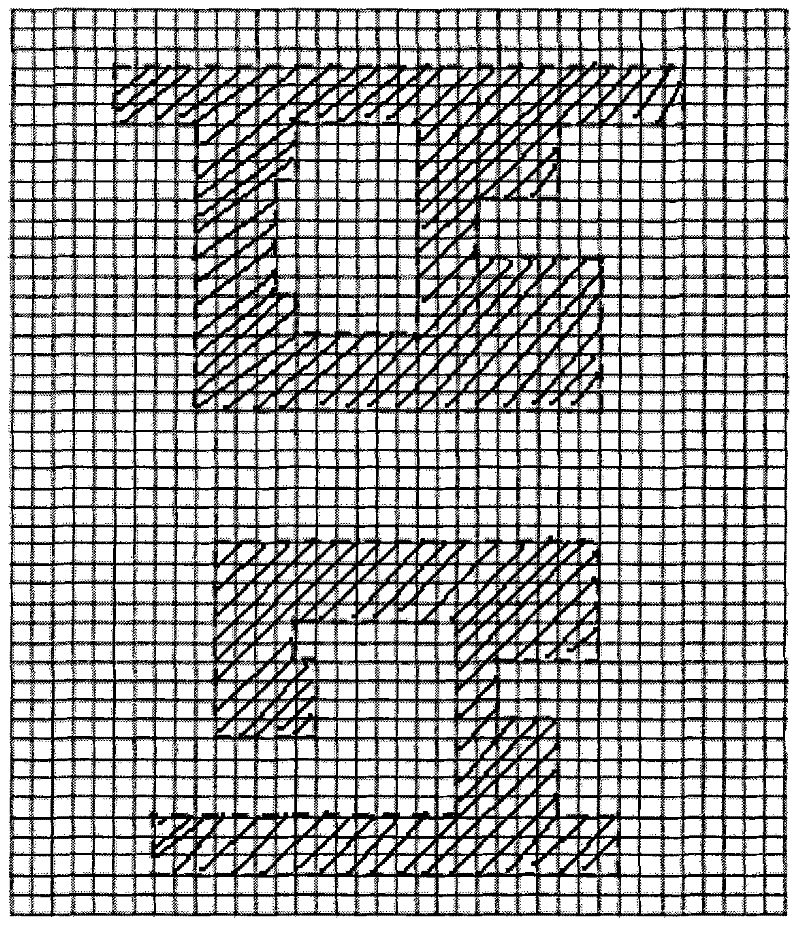

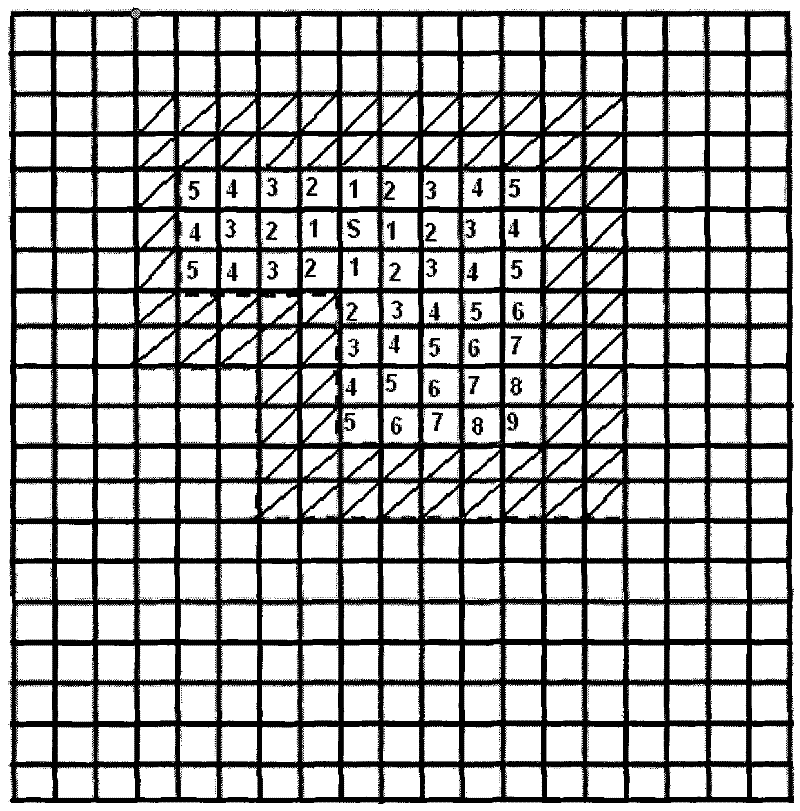

[0027] 1. After the chip design rules are integerized, the greatest common divisor λ of the design rules is obtained through the Stein algorithm cycle calculation; with λ as the basic unit, the layout of the standard cell polysilicon layer, active area layer, via layer and metal layer is evenly divided Form a rectangular grid, if there is no graphic on the grid point, set the grid point attribute to "0", and if there is a graphic on the grid point, set the grid point attribute to "1", ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com