High voltage low power consumption SOI LDMOS transistor having strained silicon structure

A low power consumption, transistor technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of limited interaction, super junction structure has not been widely used, and the impact of device breakdown voltage, etc., to meet the application requirements , Improving the mobility of electron carriers and reducing the drain-source on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention is described in more detail below in conjunction with accompanying drawing example:

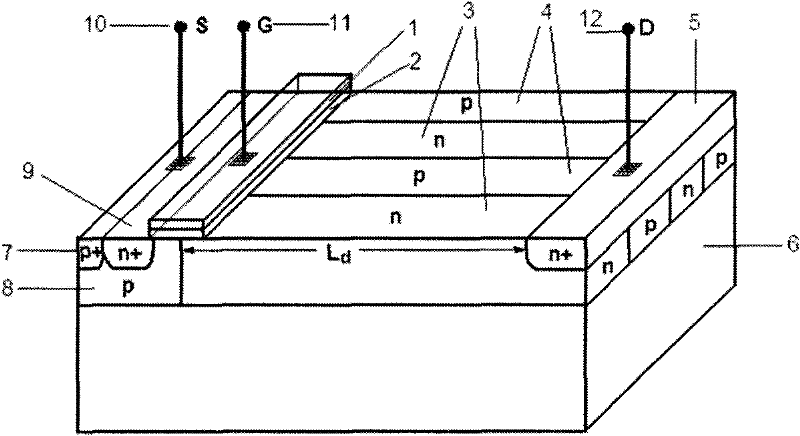

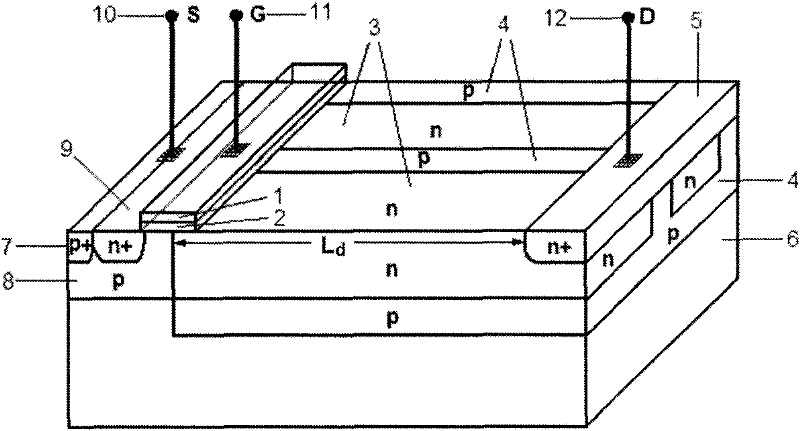

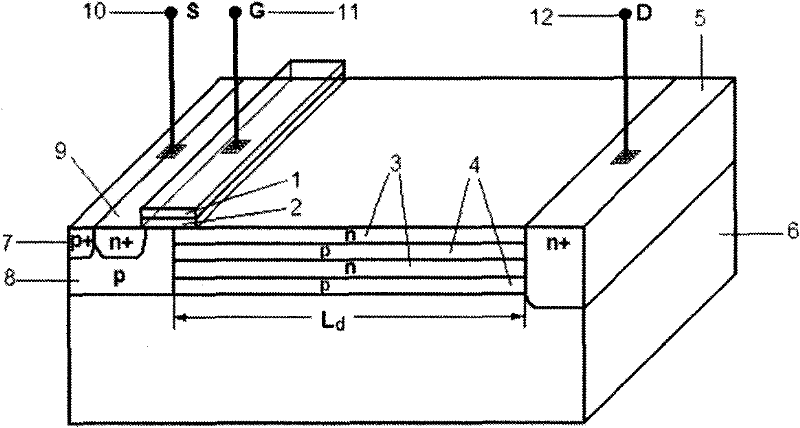

[0020] refer to figure 2 , SOI LDMOS transistor of the present invention. Including source region 9, body region 8, n-column 3 in superjunction, p-column 4 in superjunction, drain region 5, source electrode 10, drain electrode 12, gate electrode 11, buried dielectric layer 6 (SiO 2 or Al 2 o 3 and other insulating dielectric layers). It is characterized in that the p-column 4 is a single crystal material that does not match the silicon material lattice (such as Ge, SiGe and other materials that enable silicon to generate strain), and the n-column 3 is an n-type parallel to the p-column 4 generated on the basis of the p-column 4. Laterally tensile strained silicon for source and drain electrodes. In the super junction structure, the cross-section of the p-pillar 4 in the direction of the source and drain electrodes is a comb structure. According to the requi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com