Semiconductor device

A semiconductor, top-side technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of reducing the degree of freedom of the side wiring position, to improve the positional freedom, reduce the chip area, easy-to-create effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

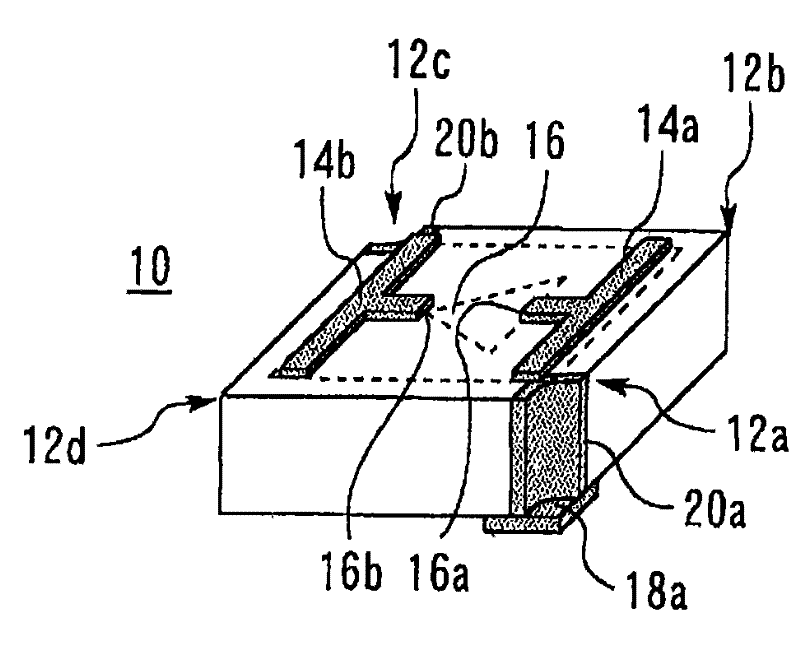

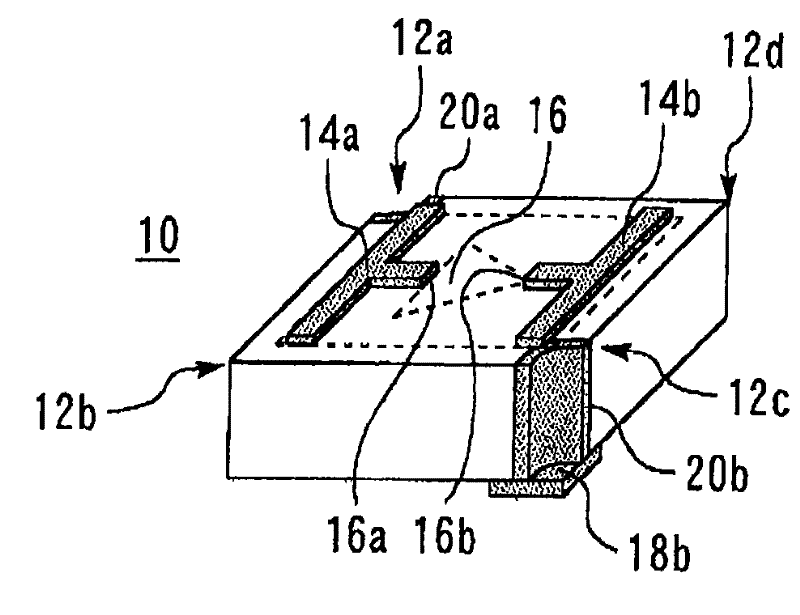

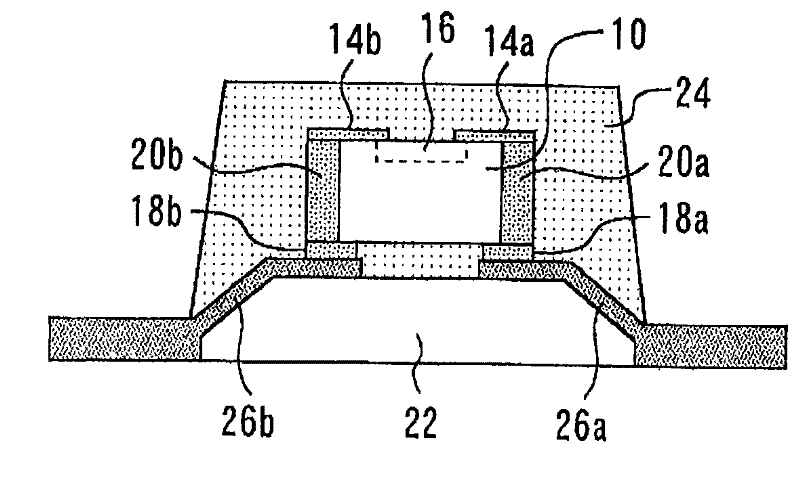

[0021] figure 1 , figure 2 It is a perspective view showing the semiconductor chip of Embodiment 1. The semiconductor chip 10 has top and bottom surfaces facing each other and side surfaces connecting the top and bottom surfaces. The top surface of the semiconductor chip 10 has a corner 12a, a corner 12b adjacent to the corner 12a, a corner 12c existing on the diagonal of the corner 12a, and a corner existing on the diagonal of the corner 12b. The quadrilateral of part 12d.

[0022] On the top surface of the semiconductor chip 10, a top wiring 14a is formed to connect the corner 12a and the corner 12b, and a top wiring 14b is formed to connect the corner 12c and the corner 12d. Electronic circuitry 16 is formed on the top surface of semiconductor chip 10 . The electronic circuit 16 has an input terminal 16b connected to the top wiring 14a and an output terminal 16a connected to the top wiring 14b. Bottom electrode 18a is formed at a corner of the bottom surface correspon...

Embodiment approach 2

[0037] Figure 7 It is a perspective view showing the semiconductor chip of Embodiment 2. The semiconductor chip 10 has top and bottom surfaces facing each other and side surfaces connecting the top and bottom surfaces. The top surface of the semiconductor chip 10 is quadrangular.

[0038] On the top surface of the semiconductor chip 10 , top surface wiring 14 is formed along the outer periphery of the top surface. Electronic circuitry 16 is formed on the top surface of semiconductor chip 10 . The electronic circuit 16 has an input terminal 16 b connected to the top surface wiring 14 and an output terminal 16 a connected to the lead pad 36 . A bottom electrode 18 is formed on the bottom surface of the semiconductor chip 10 .

[0039] A side wiring 20 is formed on a side surface of the semiconductor chip 10 . The side wiring 20 connects the top wiring 14 and the bottom electrode 18 . The input terminal 16 b of the electronic circuit 16 is connected to the side wiring 20 v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com