Power-on reset control circuit and operation method thereof

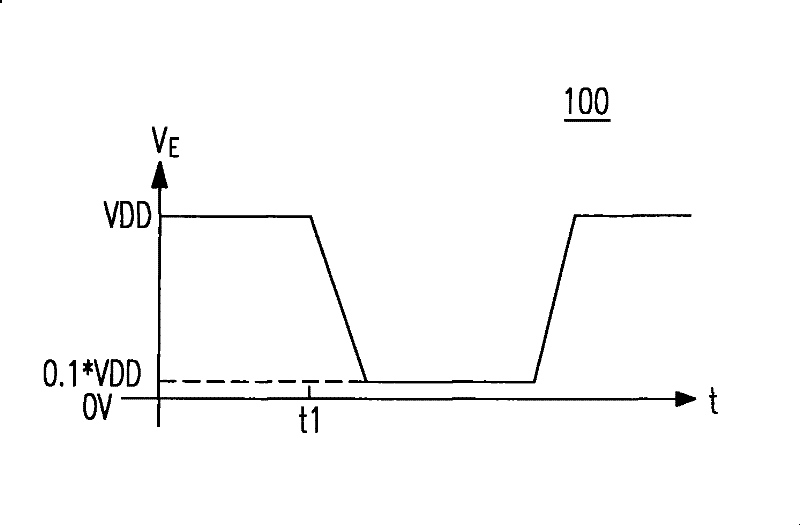

A technology for turning on the power supply and controlling the circuit, which is applied in the direction of electronic switches, data processing power supplies, measuring devices, etc., and can solve the problem that the reset signal is not generated.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

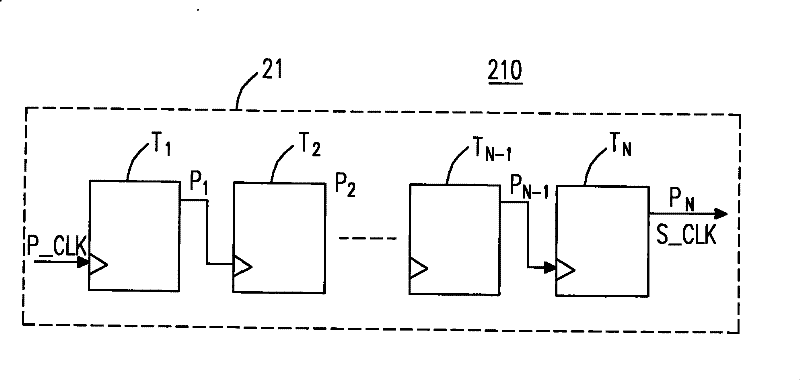

[0025] The circuit design concept is based on the idea that the necessary condition for the chip (IC) to work is that the clock must start to oscillate. The RC oscillator or crystal (Crystal) oscillator is used to start oscillating the initial oscillation signal related to the voltage, and the frequency divider is shifted to The bit register sends a stable shift clock signal, and the level that starts to shift the register is sequentially shifted and supplemented in a first-in-first-out manner, and the output of the last stage of the shift register is used as a power-on reset signal.

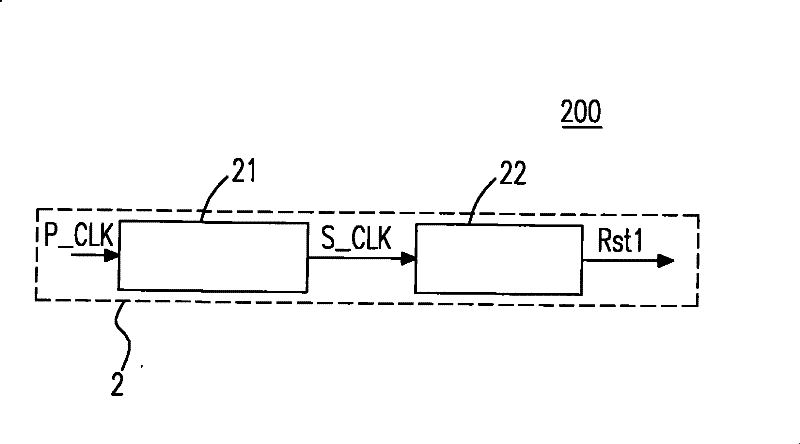

[0026] Please refer to FIG. 2( a ), which is a structural diagram of a digital power-on-reset generating circuit 2 . The digital power-on-reset generating circuit 2 includes a frequency divider 21 and a first shift register 22 . When the first voltage rises to the starting voltage, the oscillator (not shown) starts to generate the oscillation signal P_CLK, the frequency divider 21 receives the os...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com