Lateral diffused metal oxide semiconductor transistor structure capable of avoiding double-hump effect

An oxide semiconductor and transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of transistor leakage, low turn-on voltage, low turn-on voltage, etc., and achieve the effect of constant threshold voltage Vt and uniform thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to better understand the technical content of the present invention, specific embodiments are given together with the attached drawings for description as follows.

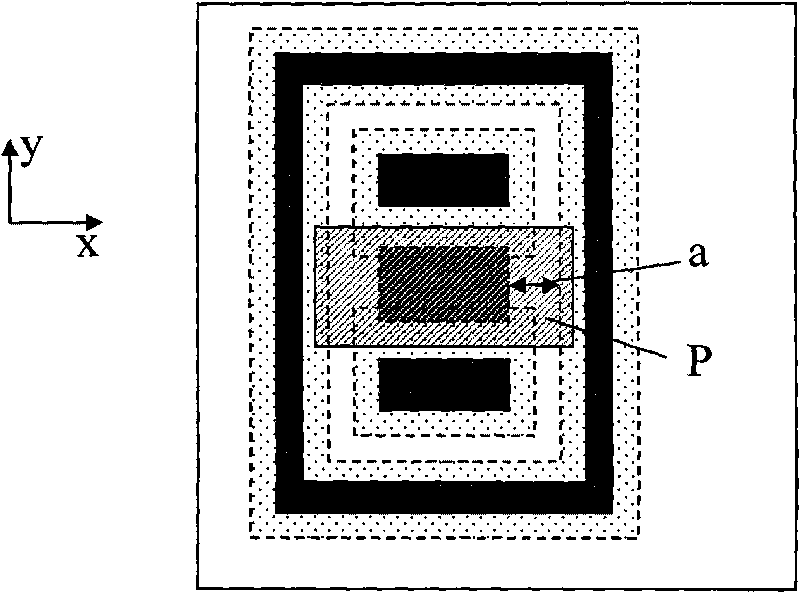

[0022] Figure 4 It is a schematic top view of the LDNMOS structure disclosed in the present invention; Figure 5 for Figure 4 Schematic cross-sectional view of the LDNMOS structure along the x direction; Figure 6 for Figure 4 A schematic cross-sectional view of the LDNMOS structure along the y direction.

[0023] Please also refer to Figure 4~6 In this embodiment, the LDNMOS structure includes a base layer B, an oxide layer GOX, and a polysilicon layer P in order from bottom to top.

[0024] In this embodiment, the base layer B is an N well, and the polysilicon layer P formed thereon serves as the gate G of the LDNMOS. On both sides of the oxide layer GOX in the base layer B, there are corresponding N-type drift regions N-d as the source S and drain D of the LDNMOS.

[0025] The N-type ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com