High-speed LDPC code coder and coding method thereof

A technology of LDPC codes and encoders, which is applied in the field of high-speed LDPC codes and encoders, and can solve the problems of increased computational and storage complexity, impracticality, and inability to guarantee the sparsity of the generator matrix.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

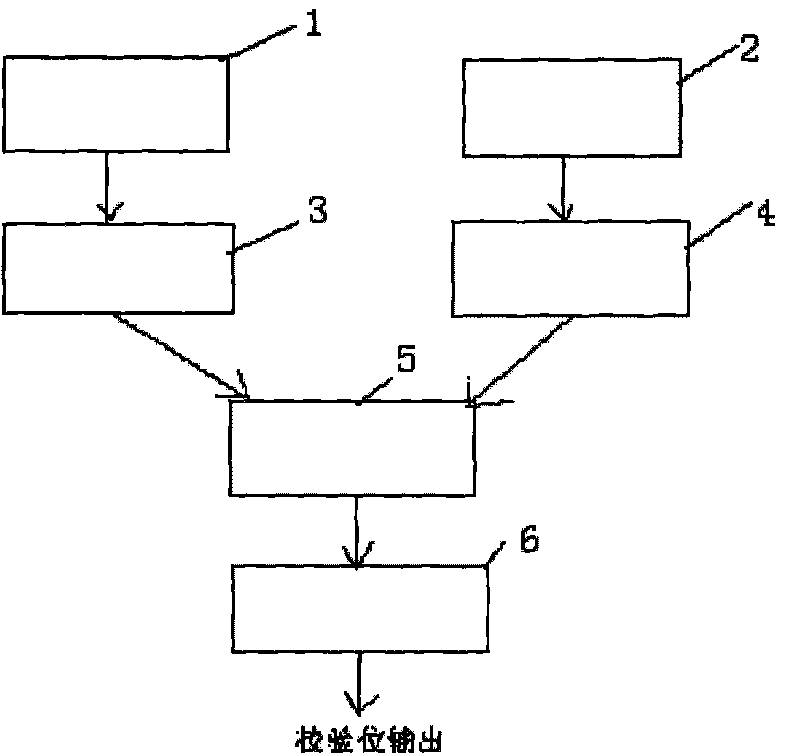

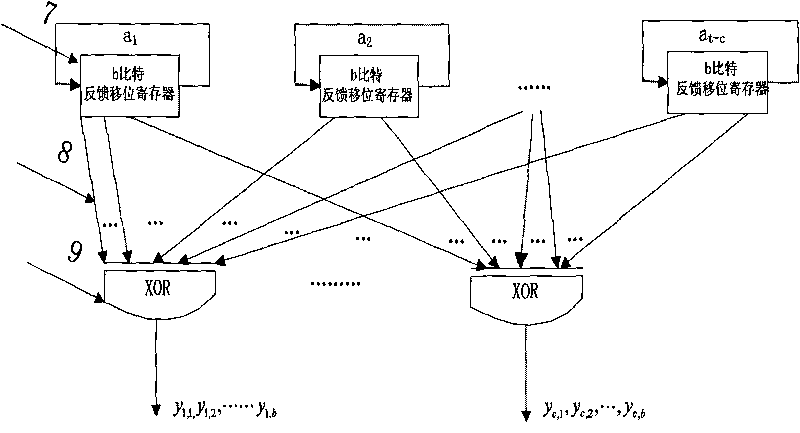

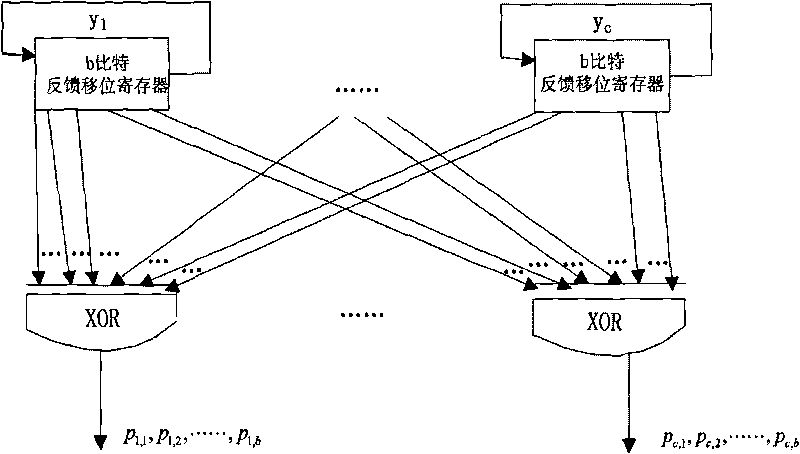

[0085] Such as figure 1As shown, a high-speed LDPC code encoder includes primary encoding circuits 1 and 2, secondary encoding circuit 6, temporary storage modules 3 and 4 and control module 5, primary encoding circuits 1, 2 and secondary encoding circuit 6 It contains a feedback shift register and an exclusive OR gate, and the first-level encoding circuits 1 and 2 obtain intermediate vectors according to the check matrix and information bits, and the temporary storage modules 3 and 4 are register groups, which are characterized in that two-way first-level encoding circuits 1, 2 The output terminal of 2 is connected to the register input terminals in the two temporary storage modules 3 and 4, and the output terminal of the registers in the temporary storage modules 3 and 4 passes through the control module 5 and the input terminal of the feedback shift register of the secondary encoding circuit 6 connected, the secondary encoding circuit 6 obtains the check bit according to th...

Embodiment 2

[0088] A method of encoding using the above encoder, such as Figure 1-5 As shown, the steps are as follows:

[0089] 10. In the first clock cycle, the control module 5 controls the primary encoding circuit ① to start working, the primary encoding circuit ② and the secondary encoding circuit wait, and the It is known that at this time, it is equivalent to l=1, and y is obtained through the calculation of the first-level encoding circuit ① 1,1 ,y 2,1 ,...y c,1 , and store these c bits into the 0th bit of the feedback shift register of c of the temporary storage module 3;

[0090] 11. In the second clock cycle, the control module 5 controls the primary encoding circuit ① to stop working, the primary encoding circuit ② starts to work, and the primary encoding circuit ② calculates y 1,2 ,y 2,2 ,...y c,2 , respectively stored in the first bit of each feedback shift register in the temporary storage module 4;

[0091] 12. In the third clock cycle, the first-level encoding ci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com