Bus monitoring method and apparatus based on AHB bus structure

A technology of monitoring device and bus structure, applied in the direction of instruments, digital data processing, memory systems, etc., can solve the problem of the lack of mature implementation methods and examples of bus monitoring technology, so as to avoid deadlock and ensure consistency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

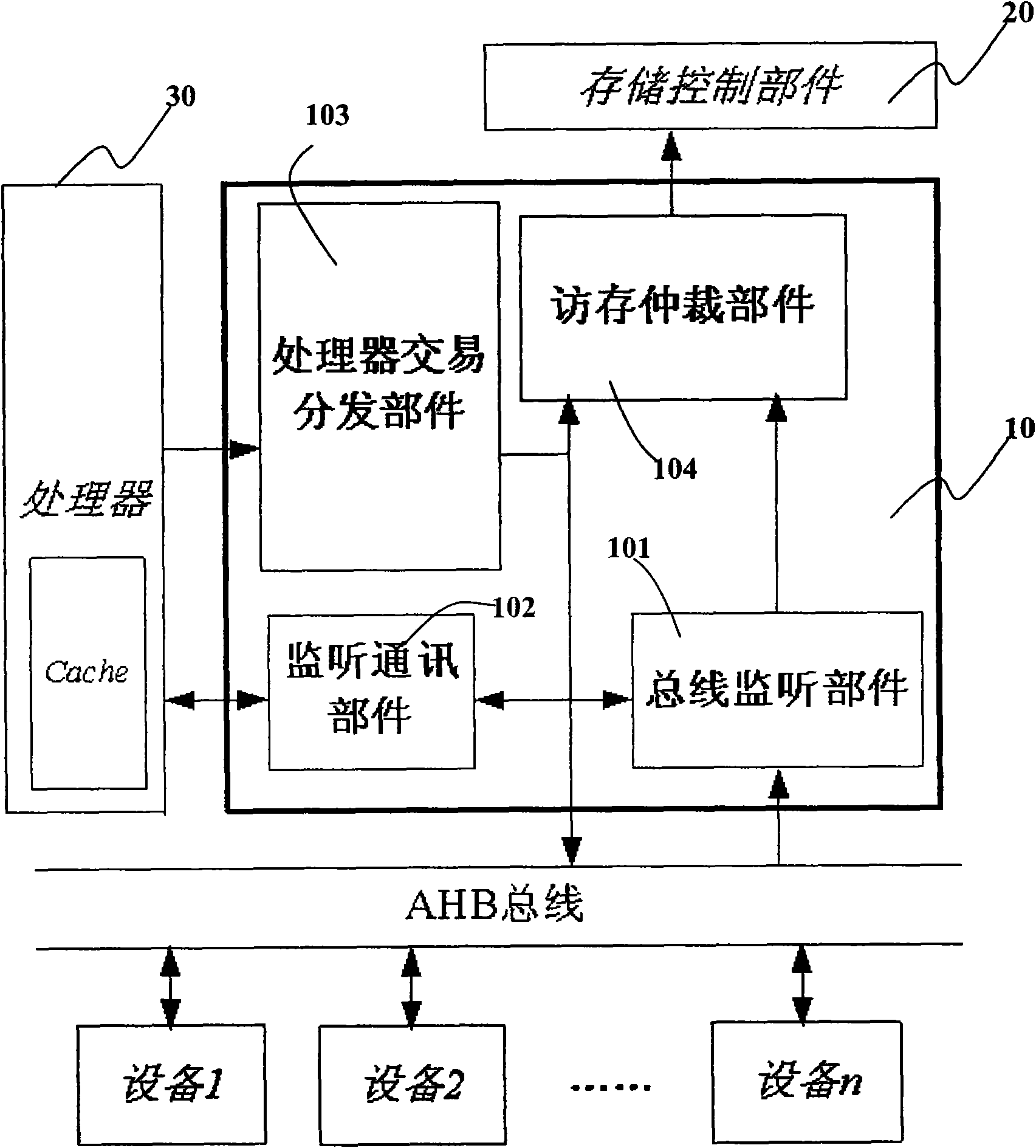

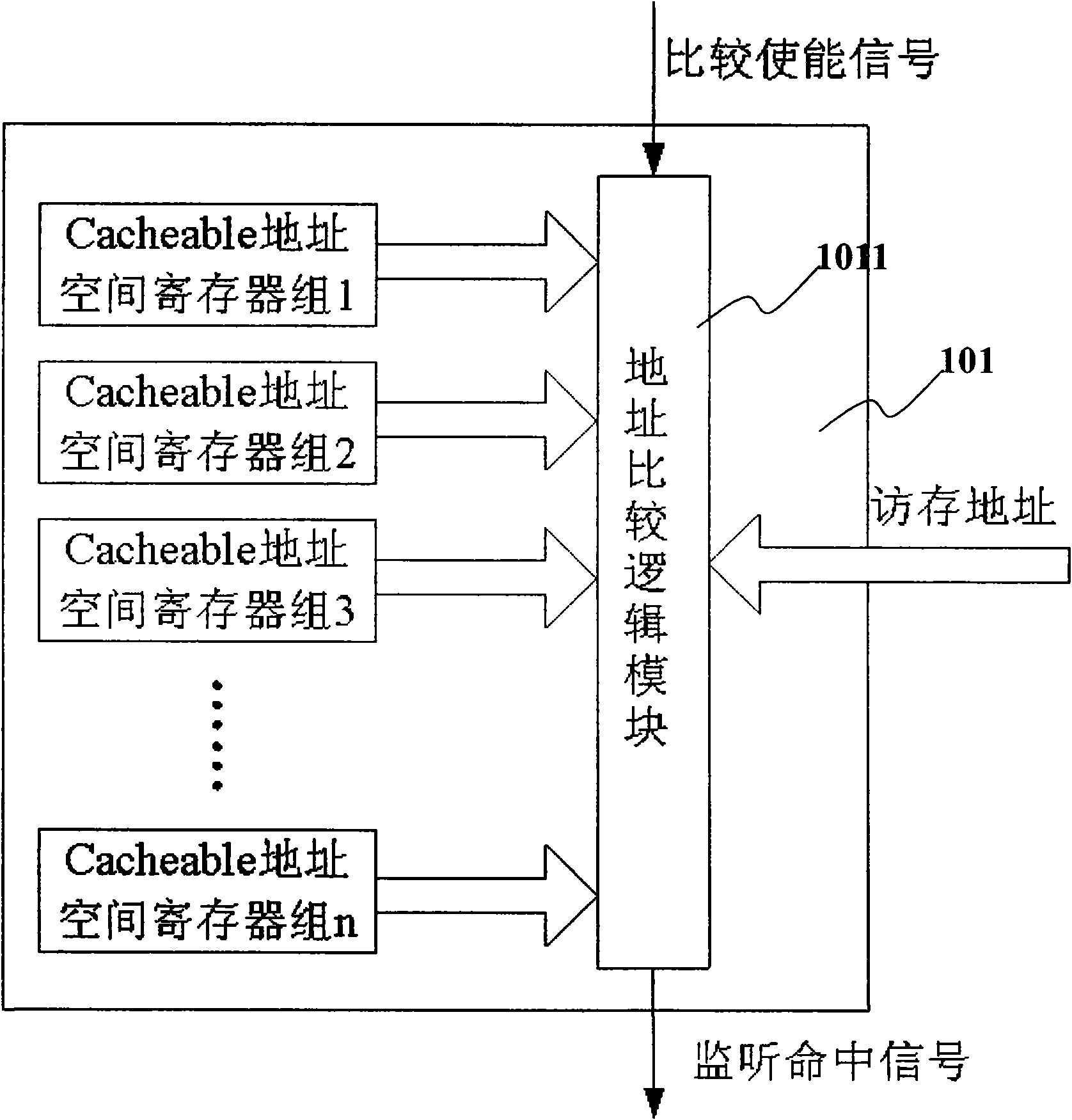

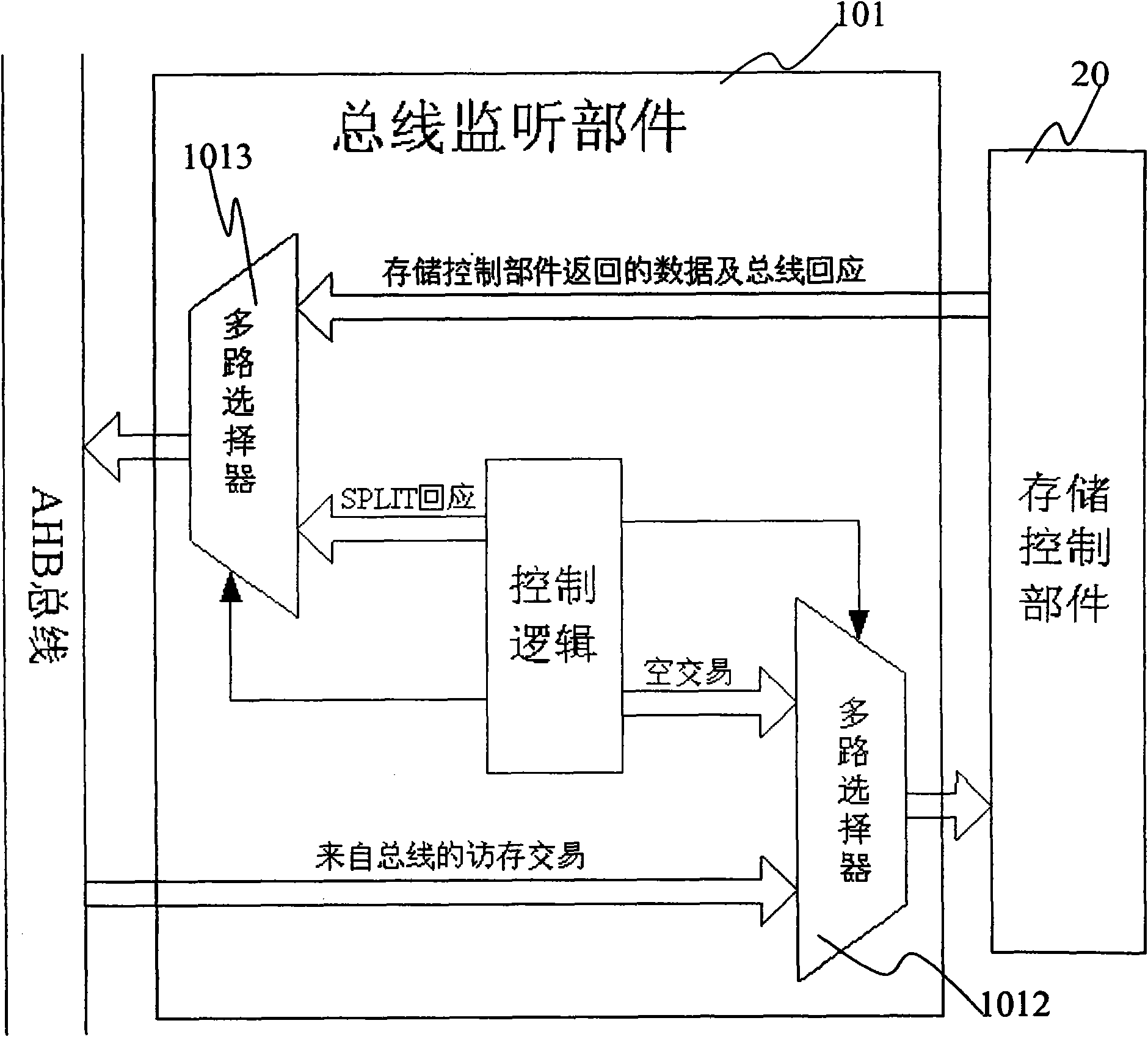

[0042]The present invention is aimed at a single processor system, only the Cache in the processor keeps a copy of the main memory data, so in order to ensure the consistency of the Cache, it is only necessary to monitor the request of the bus master to access the main memory, and for the request of the processor to access the main memory No monitoring is required. The essence of the present invention is that a bus monitoring device is added between the storage control unit and the bus to filter memory access requests issued by the bus master. If the memory access request may affect the Cache consistency, the processor is notified to carry out the Cache consistency processing, and after the consistency processing ends, the bus monitoring device is notified to allow the request to access the storage control unit; if the memory access r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com