Multi-DSP core framework and method for rapidly processing parallel video signal

A technology of video signal processing and parallel processing, applied in the direction of digital video signal modification, television, image communication, etc., can solve the problems of large data flow of data bus and increased processing time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

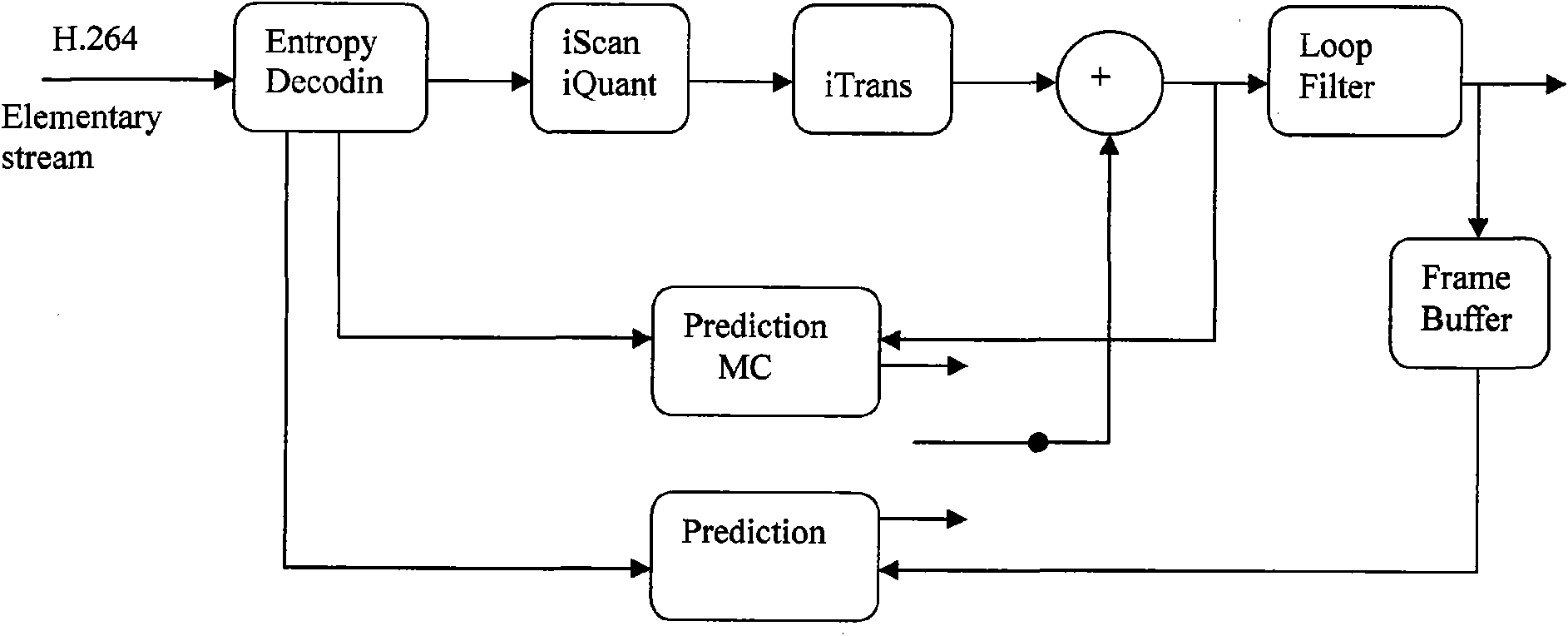

[0025] The method of the present invention can be applied to various video formats, such as H.264, MPEG2 / 4, JPEG, VC, AVS, etc.; it is also applicable to processing other real-time signals such as communication data by multiple DSP cores.

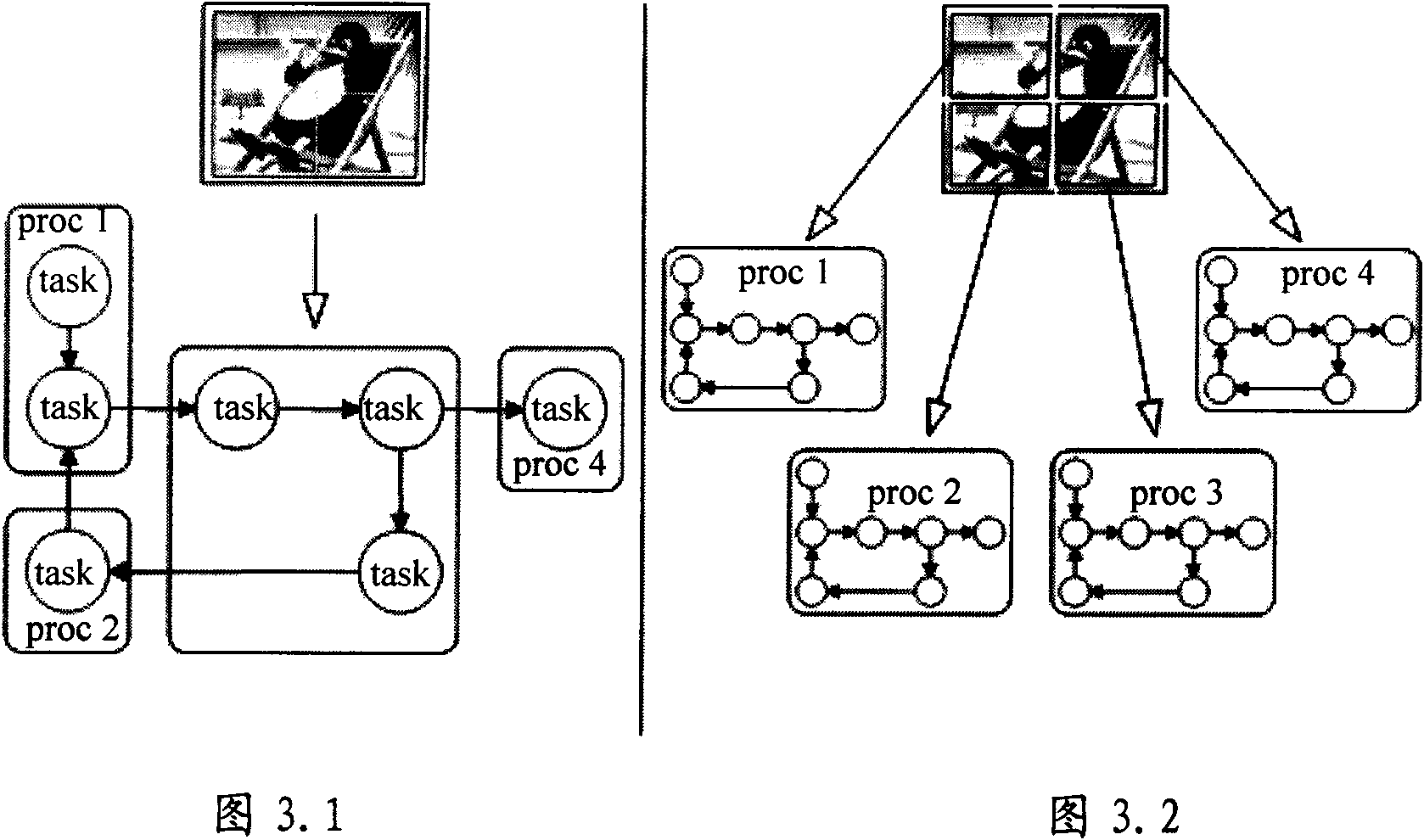

[0026] The serial and parallel (pipeline) processing referred to in the present invention refers to the first step of processing the first frame of image by the first DSP core. After it has been processed, it is handed over to the next DSP core for the second step, and then goes to it by itself. Do the first step of the next frame of image; and after the second DSP core processes the second step, hand it over to the next DSP core for the third step, and then do the second step of the next frame of image by yourself; proceed like this.

[0027] The term “parallel processing” in the present invention means that multiple DSP cores simultaneously process different parts of the image in one step for the same frame of image.

[0028] In the following...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com