Wafer level fan-out chip packaging structure

A chip packaging structure, wafer-level technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problem of low packaging cost, achieve the effect of reducing packaging cost and solving chip displacement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

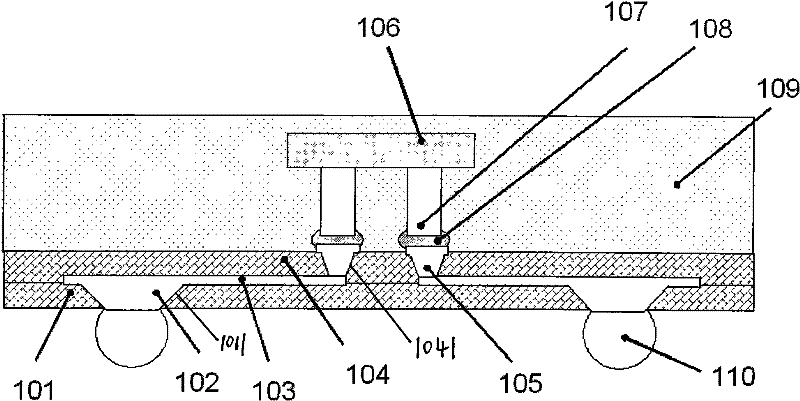

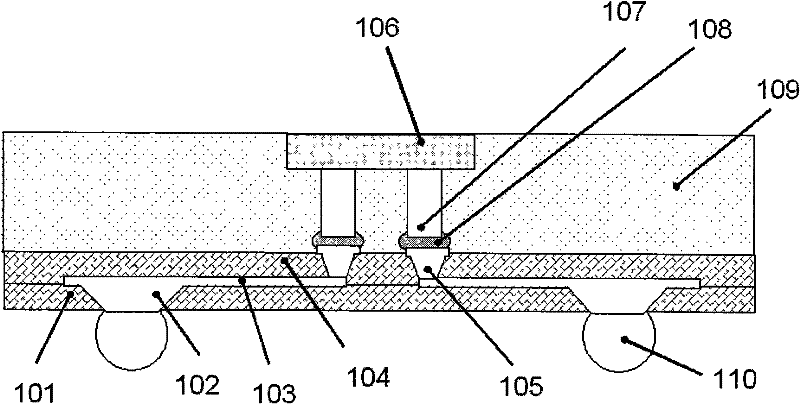

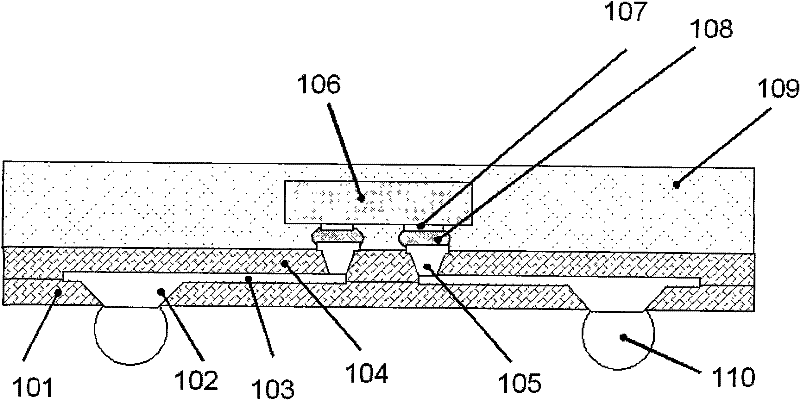

[0019] see figure 1 , the wafer-level fan-out (Fanout) chip packaging structure of the present invention includes a thin-film dielectric layer I 101, and a photolithographic pattern opening I 1011 is formed on the thin-film dielectric layer I 101, and the pattern opening I 1011 and the thin-film dielectric layer The surface of I 101 is provided with a metal electrode 102 connected to the substrate end and a redistribution metal trace 103, and the surface of the metal electrode 102 connected to the substrate end, the redistribution metal trace 103 surface, and the surface of the thin film dielectric layer I 101 are covered with Thin-film dielectric layer II104, on which a photolithographic pattern opening II 1041 is formed, and a metal electrode 105 connected to the chip end is arranged on the photolithographic pattern opening II 1041, which will have an IC chip 106, The chip of metal post / metal bump 107 and solder 108 is flip-chip mounted on the metal electrode 105 connected t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com