Method for packaging semiconductor with cavity

A packaging method and semiconductor technology, which are applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as difficulty in uniformly coating barrier layers, unstable physical properties, and contamination of chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to describe in detail the steps and flow characteristics of the present invention, the following preferred embodiment is given and described as follows in conjunction with the accompanying drawings, wherein:

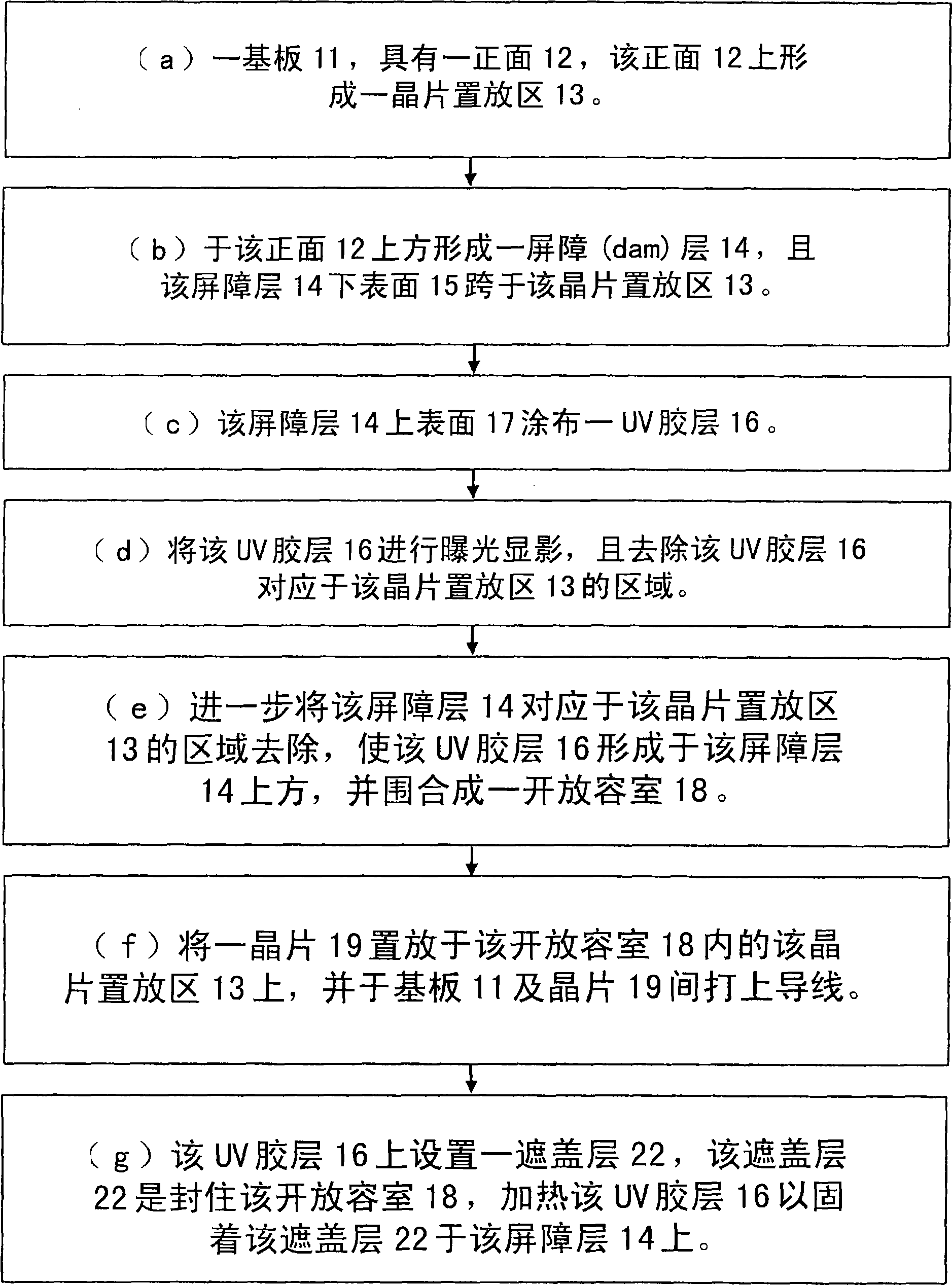

[0039] figure 1 It is an action flowchart of a preferred embodiment of the present invention;

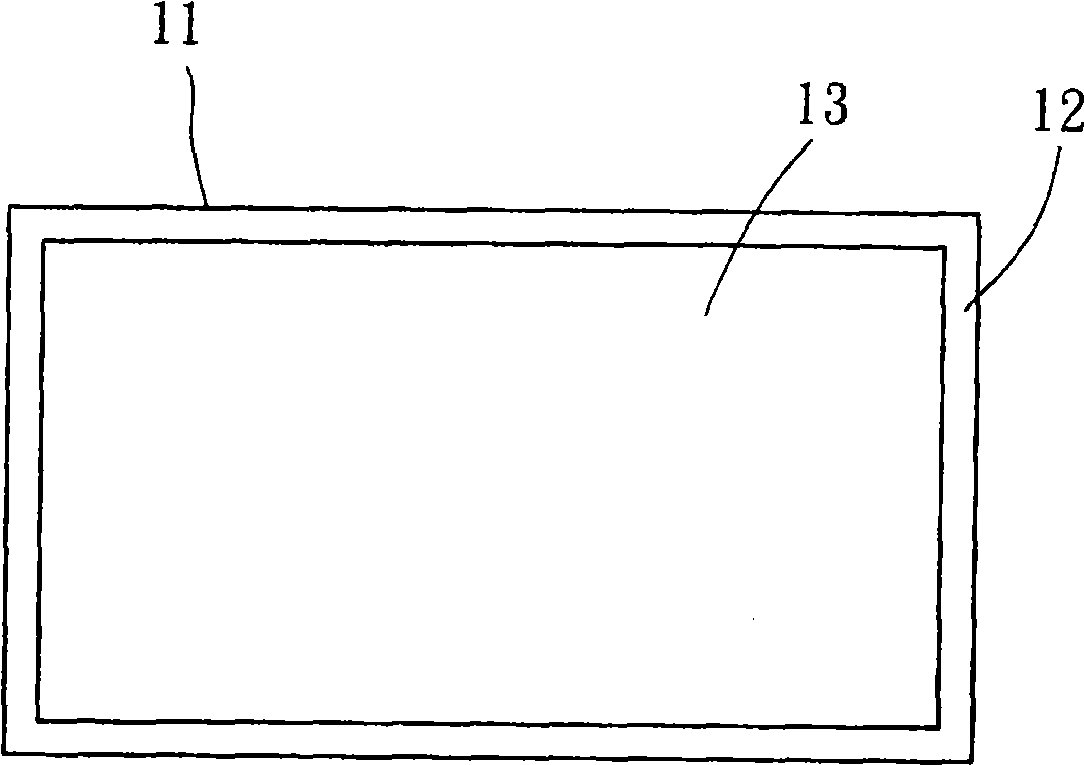

[0040] Figure 2 (A) is a schematic diagram of a preferred implementation step of the present invention, which shows the configuration of the chip placement area on the substrate;

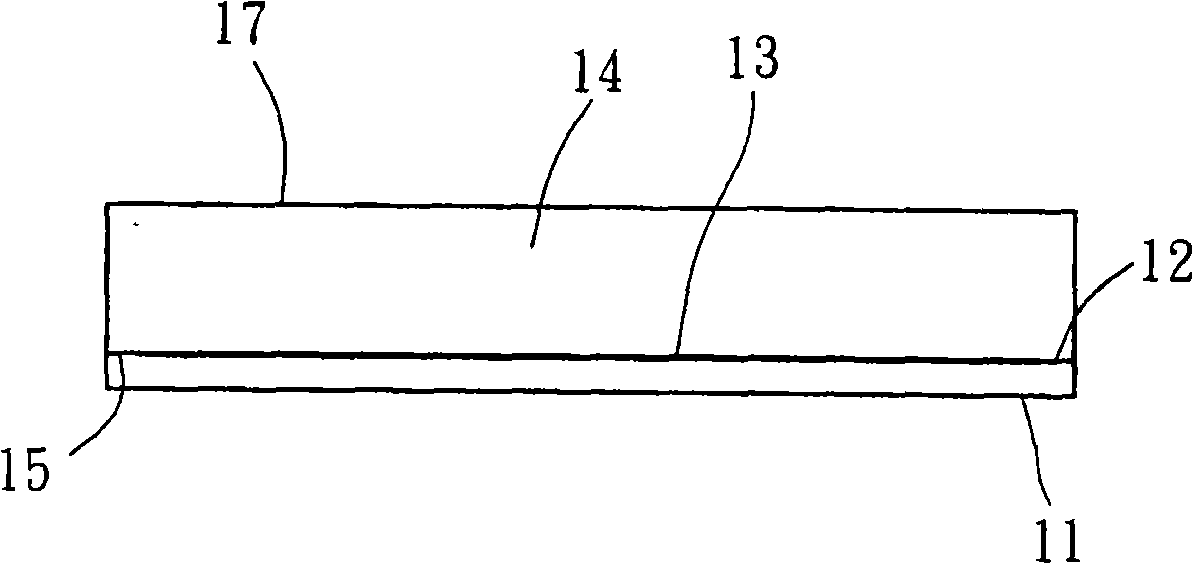

[0041] FIG. 2(B) is a schematic diagram of a preferred implementation step of the present invention, which shows the appearance of the substrate and the barrier layer when they are stacked;

[0042] Fig. 2 (C) is a schematic diagram of a preferred implementation step of the present invention, which has shown the pattern of coating UV adhesive layer above the barrier layer;

[0043] Fig. 2 (D) is a schematic diagram of a preferred implementation step of the present invention, which ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com