Realization method for supporting high-speed buffer of hardware database on chip

A high-speed buffer and data buffering technology, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of relatively large differences in buffer design and implementation, and achieve short response time, high efficiency, and improved throughput. Effect

Inactive Publication Date: 2010-12-01

ZHEJIANG UNIV

View PDF0 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The basic principle of buffering is to temporarily store data and communicate asynchronously, but the design and implementation of buffering are quite different. The buffering settings between specific devices are generally set according to the characteristics of the devices.

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

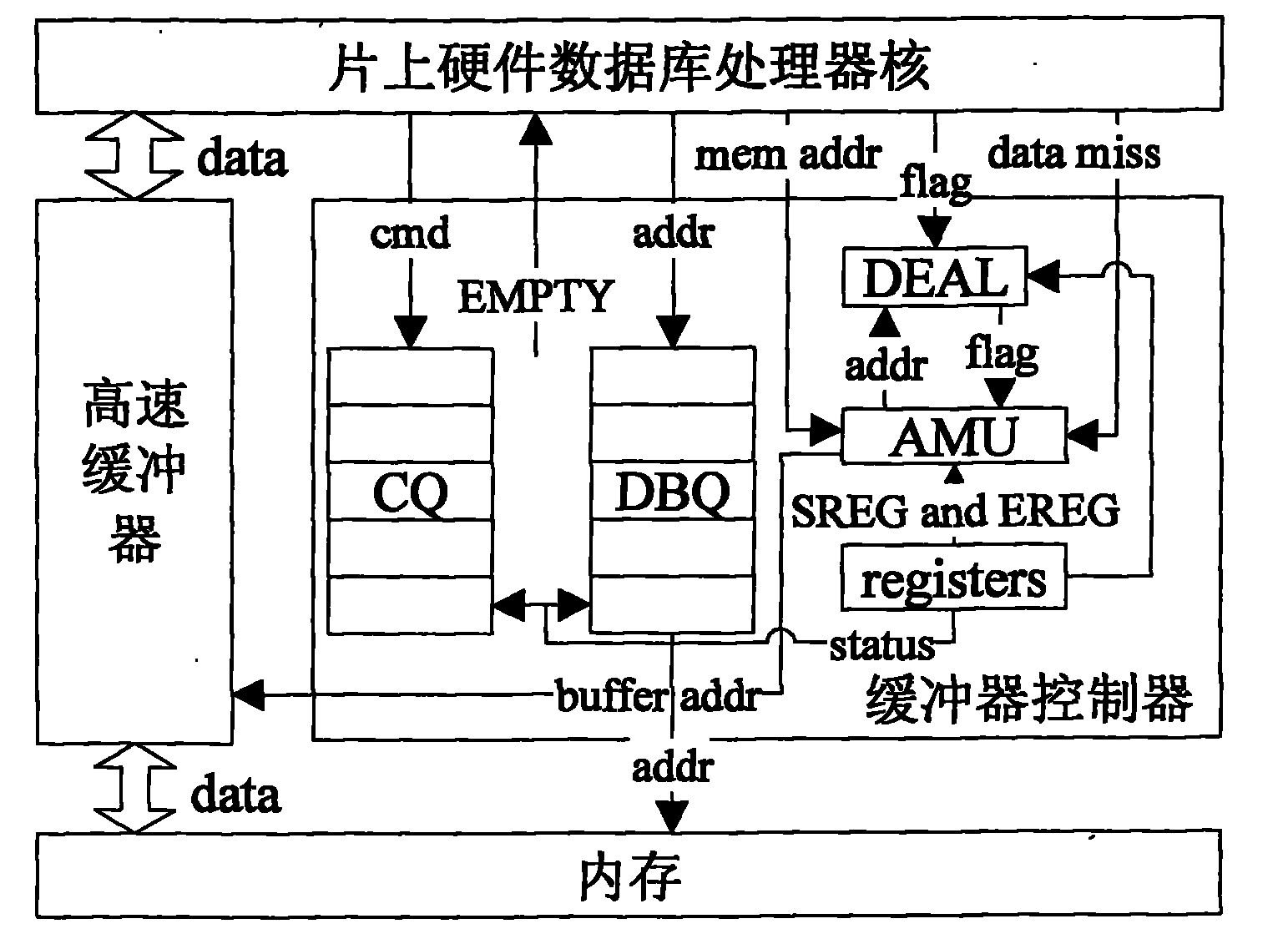

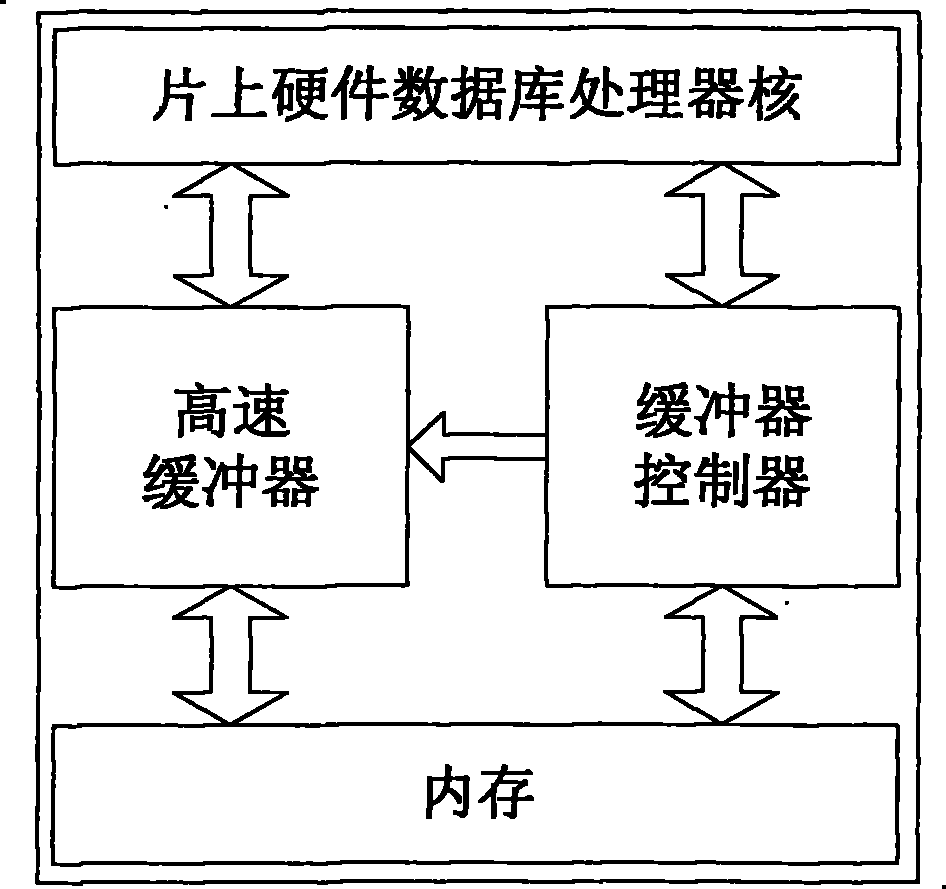

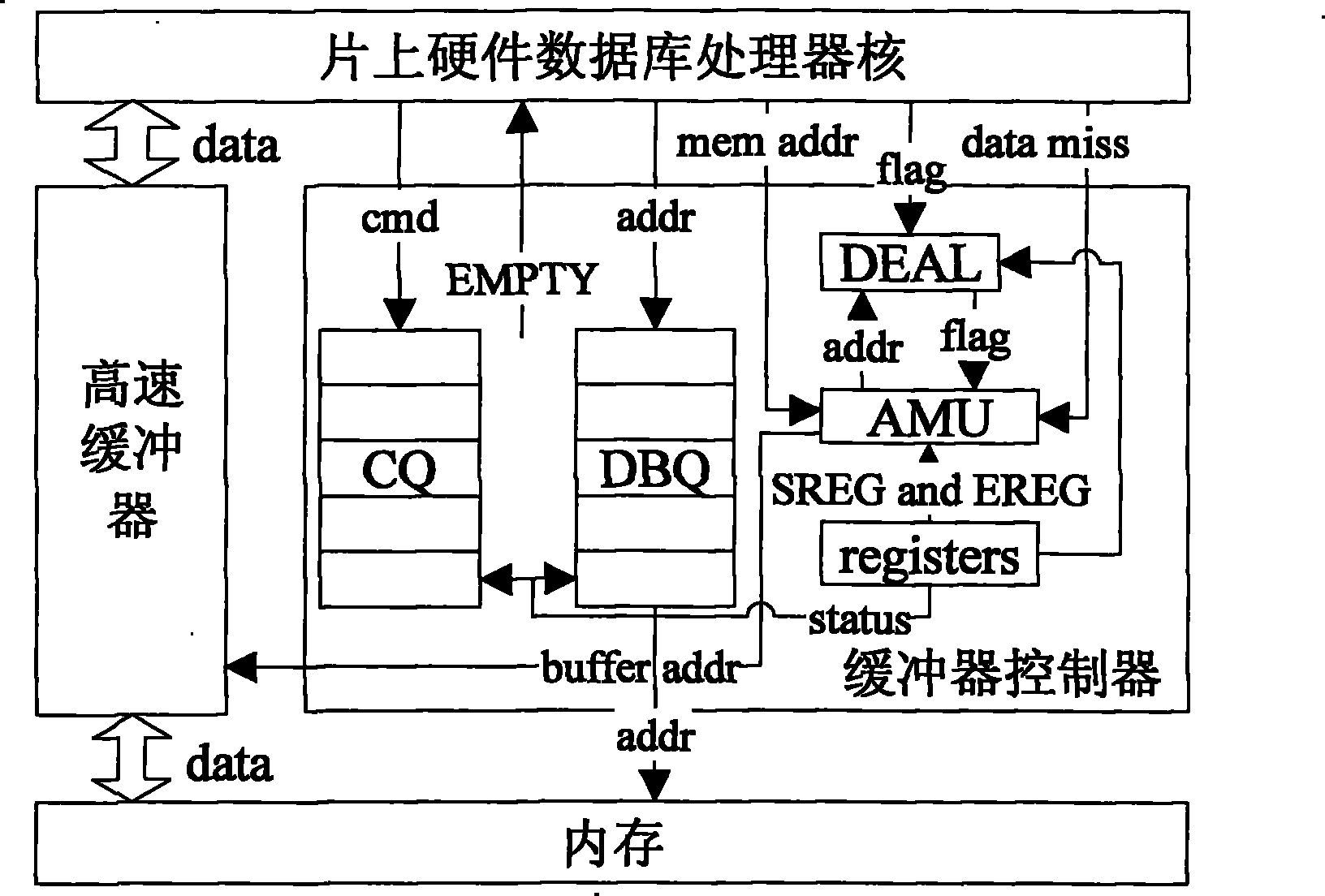

The invention discloses a realization method for supporting the high-speed buffer of the hardware database on a chip. A high-speed buffer and a buffer controller are increased between the processor core and a memory of the hardware database on a chip. The high-speed buffer can store the data and the instruction of memory accessed by a database processor and is connected with the database processor and the memory. The buffer controller is a control logic and can control the data exchange between the high-speed buffer and the database processor core and between the high-speed buffer and the memory, the buffer controller can receive the memory access signal from the database processor core and control the high-speed buffer and the database processor core to access the data in the high-speed buffer. The support of the high-speed buffer of the hardware database on the chip is beneficial for changing the mismatching of the hardware database processor core and the memory rate to in parallel perform the data processing of the database processor core and the access of data in the memory, thus improving the throughput and processing efficiency of the processor core, and enhancing the performance of the hardware database on the chip.

Description

Realization method of cache support for on-chip hardware database technical field The invention relates to the data communication technology between the on-chip hardware database processor core and memory, in particular to a high-speed buffer support realization method of the on-chip hardware database. Background technique Since the birth of database technology, it has taken less than half a century to form a solid theoretical foundation, mature commercial products and a wide range of application fields. Researchers continue to join, and it has become a research field that has been widely concerned. With the continuous growth of information content and the emergence of new technologies, database technology is facing unprecedented challenges. In the face of various data forms, people have proposed a variety of data models (hierarchical model, network model, relational model, object-oriented model, board structured model, etc.), and also proposed many new database technolog...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): G06F17/30G06F12/08G06F12/0875

Inventor 陈天洲蒋冠军王超缪良华汪达舟

Owner ZHEJIANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com