Conductive wire type semiconductor device and conductive wire rack thereof

A semiconductor and lead frame technology, applied in the field of semiconductor devices, can solve the problems of imperfect segmentation, difficult to predict circuit system behavior, high ground bounce noise, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The implementation of the present invention is described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

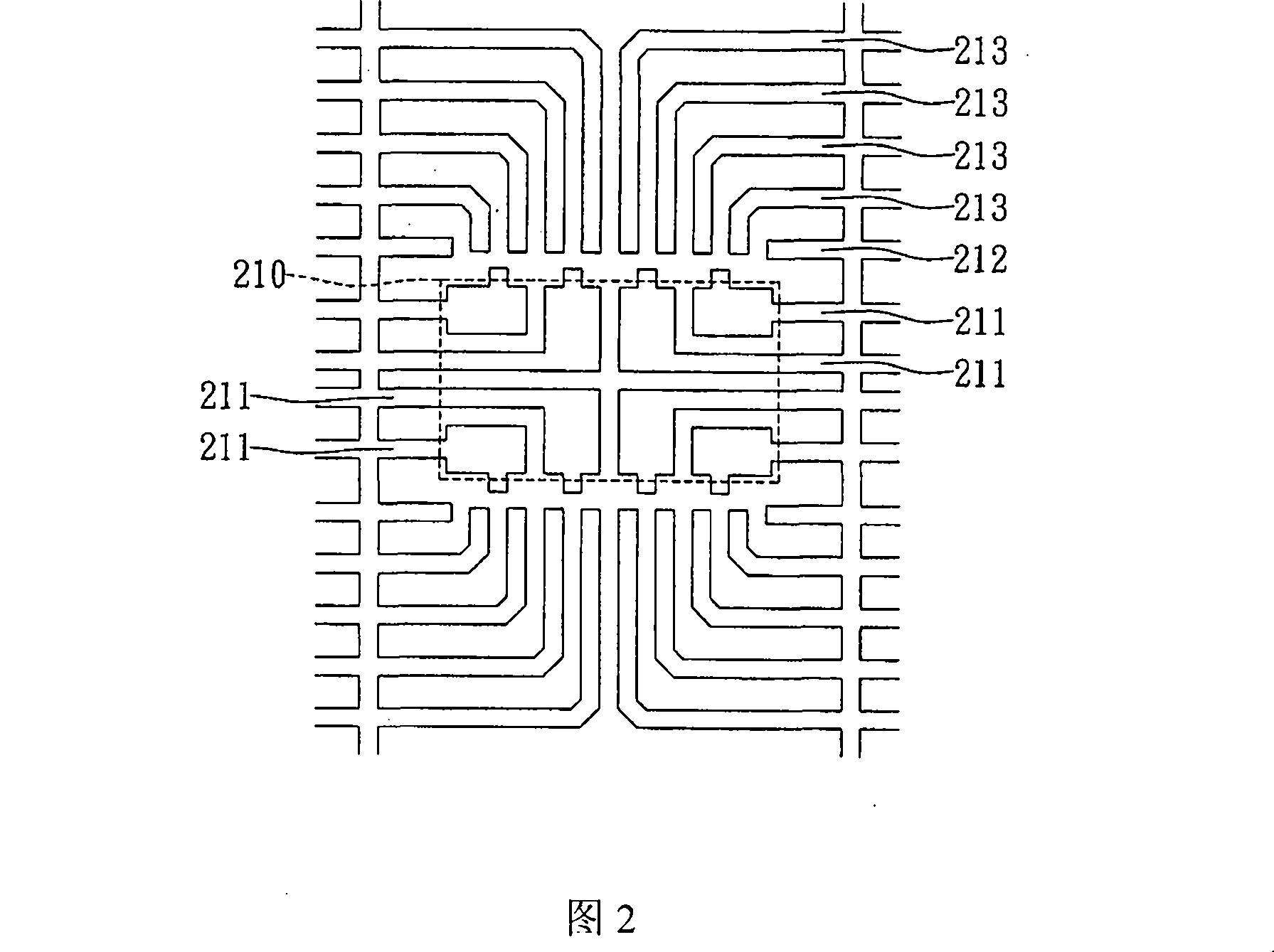

[0045] see figure 2 , is a schematic plan view of the lead frame of the present invention.

[0046] The lead frame includes a plurality of grounding pins 211, and the grounding pins 211 together form a chip placement area 210; a plurality of signal pins 213 are distributed around the chip placement area 210; and a plurality of power supply pins 212 , distributed around the chip mounting area 210 , and the size of the ground pin 211 in the chip mounting area 210 is larger than the size of the signal pin 213 and the power pin 212 .

[0047] That is, the ground pin 211 and the power pin 212 are set relatively independently to improve the ground bounce problem and strengthen the electrical function. The dimensions of the signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com