Integrated circuit structure for test

A technology of integrated circuits and test keys, which is applied to circuits, electrical components, and electrical solid-state devices, etc., can solve the problems of increased process costs, and the inability to improve the space utilization rate of the wafer's dicing lanes and manufacturing costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

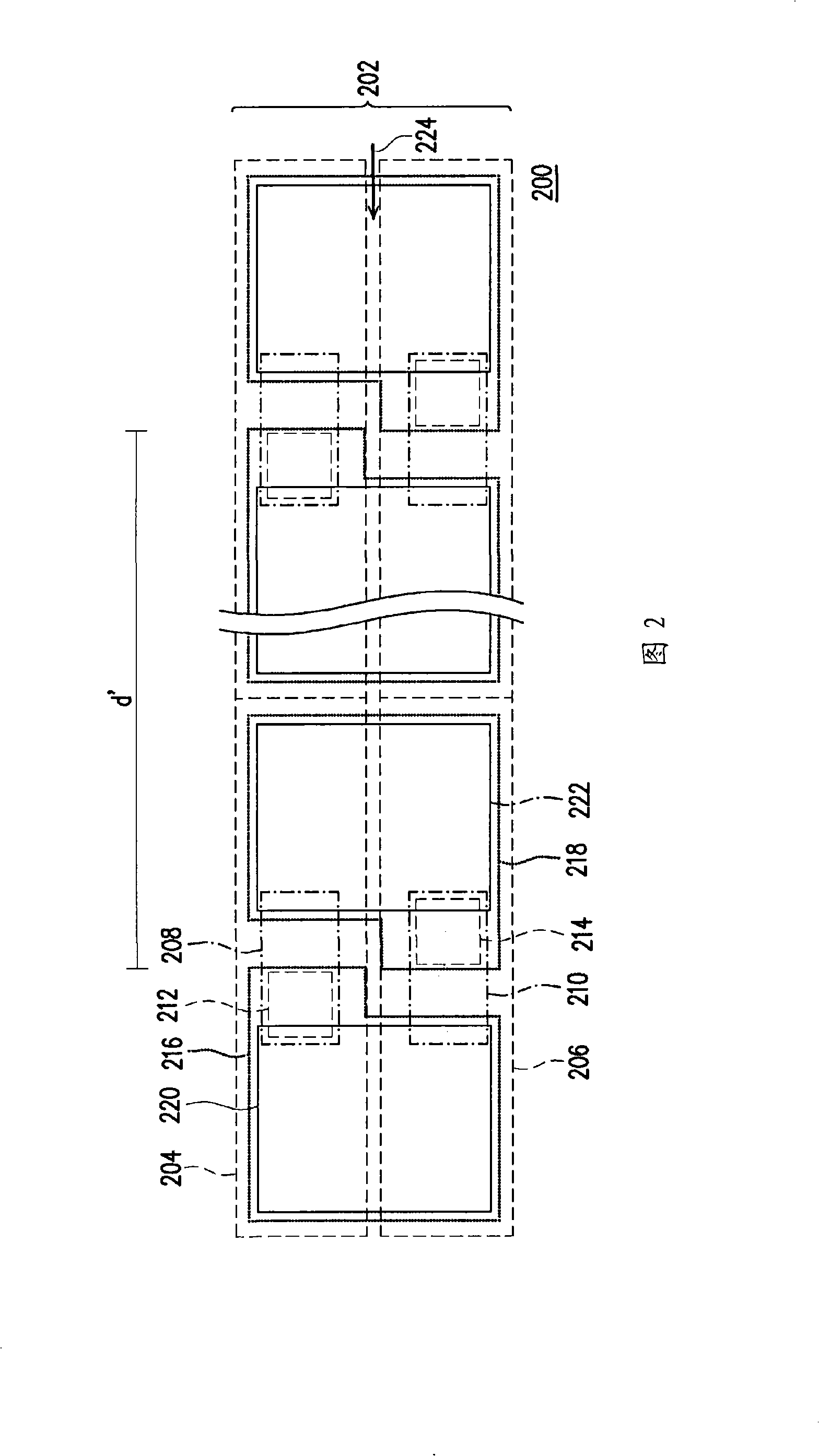

[0045] FIG. 2 is a top view of an integrated circuit structure for testing according to an embodiment of the present invention. In FIG. 2, the size and spacing of each component are all defined by current technology, and the present invention is not limited thereto.

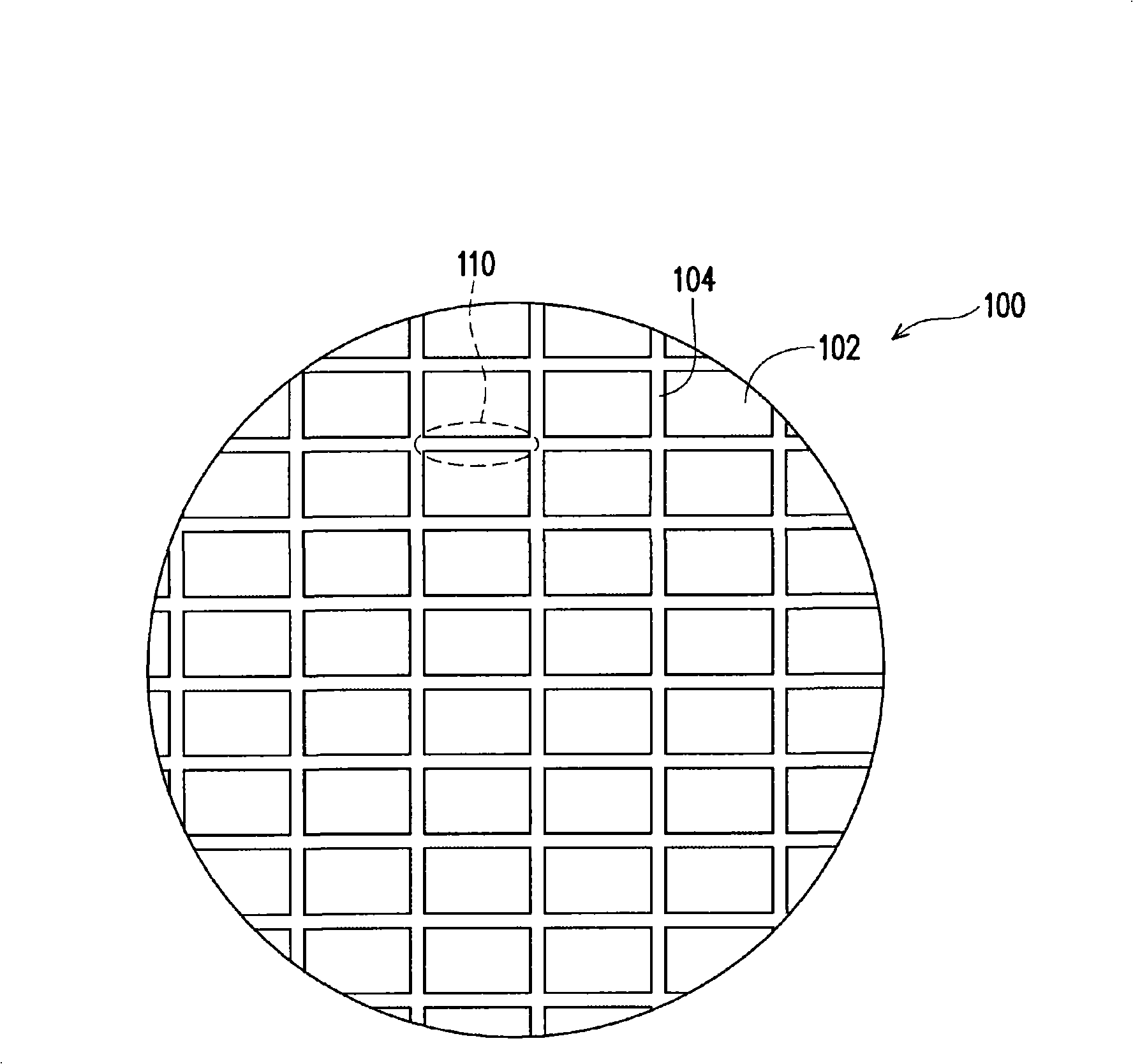

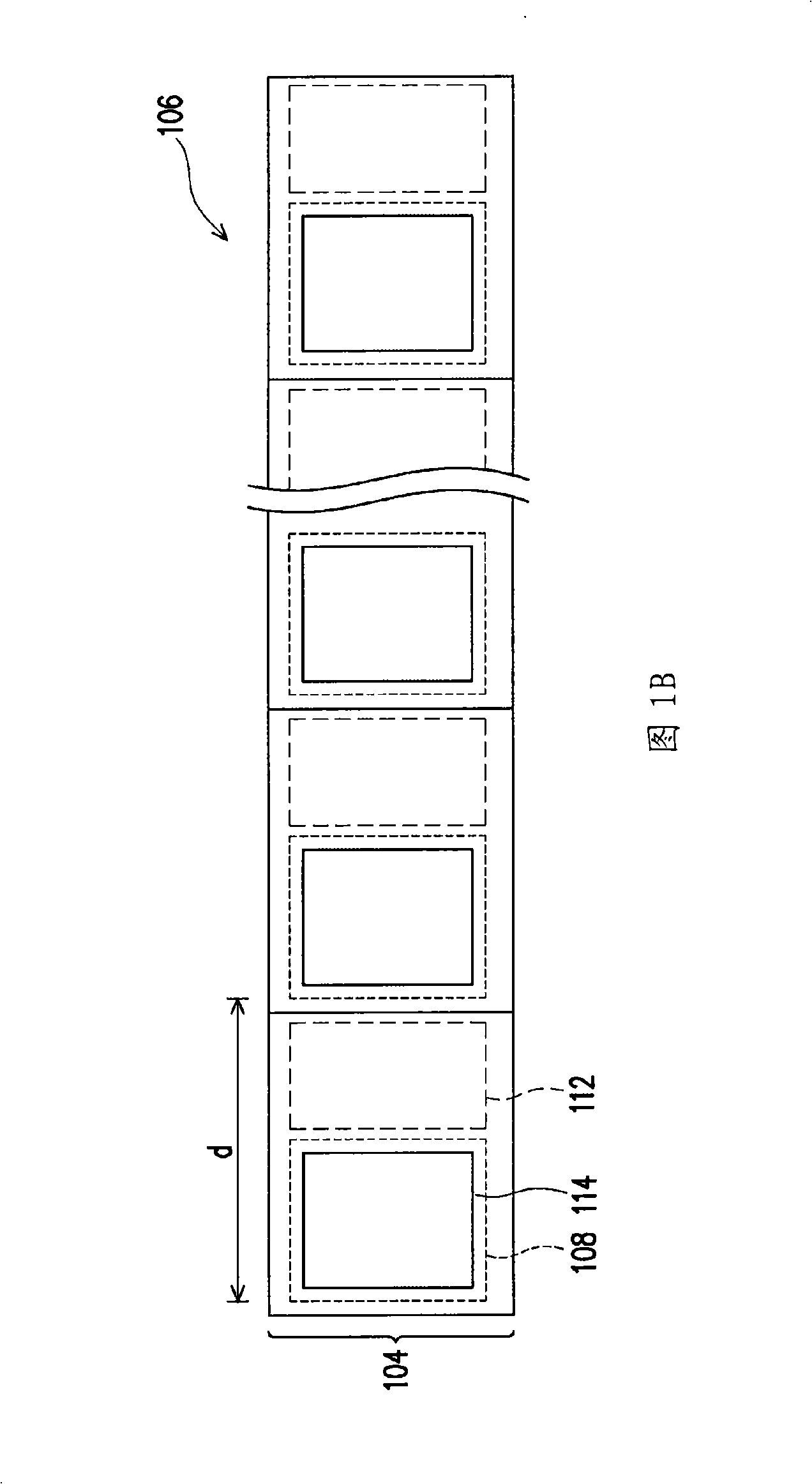

[0046] Please refer to FIG. 2, the wafer / substrate 200 has a device area (not shown) and a dicing channel area 202. Among them, the device area of the wafer / substrate 200 refers to the area of a die, which is a place where active circuit elements and interconnections are formed. The scribe area 202 refers to the area surrounding the die to separate the die. It will also be formed with similar active circuit components and interconnection structures at the same time, which is used as a test key for testing purposes. . Moreover, the manufacturing steps of active circuit elements and interconnections in the scribe zone 202 are generally integrated with the process of the element zone. The active circuit components o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com