Nanocrystalline floating gate structure non-volatility memory cell and its manufacture method

A non-volatile storage, nanocrystalline technology, applied in the field of microelectronics, can solve the problems of poor feasibility and compatibility, difficult process control, complex manufacturing process, etc., and achieve the effect of improving service life, simple structure and manufacturing process, and cost saving.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071]In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

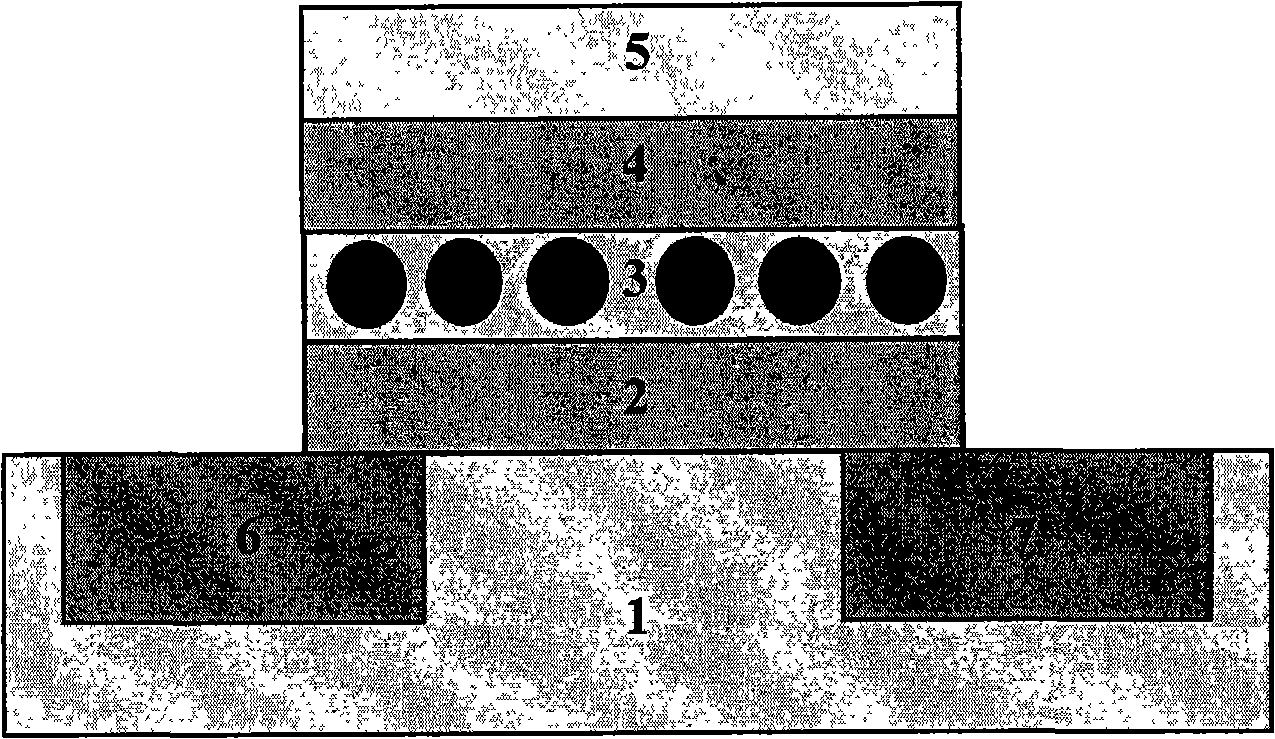

[0072] Such as figure 1 as shown, figure 1 The structure diagram of the non-volatile storage unit of the nanocrystalline floating gate structure provided by the present invention, the non-volatile storage unit of the floating gate structure includes: a silicon substrate 1, heavily doped source conductors located on both sides of the silicon substrate 1 The region 6 and the drain conduction region 7, the tunnel dielectric layer 2 covering the carrier channel between the source conduction region 6 and the drain conduction region 7, the nanocrystalline charge storage layer 3 covering the tunnel dielectric layer, covering the A control gate dielectric layer 4 on the nanocrystalline charge storage layer and a gate material lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com