LDMOS transistor

A technology of transistors and semiconductors, which is applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc. It can solve the problems of unfavorable and reduced RF power output efficiency of LDMOS transistors, and achieve the effect of reducing the total area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

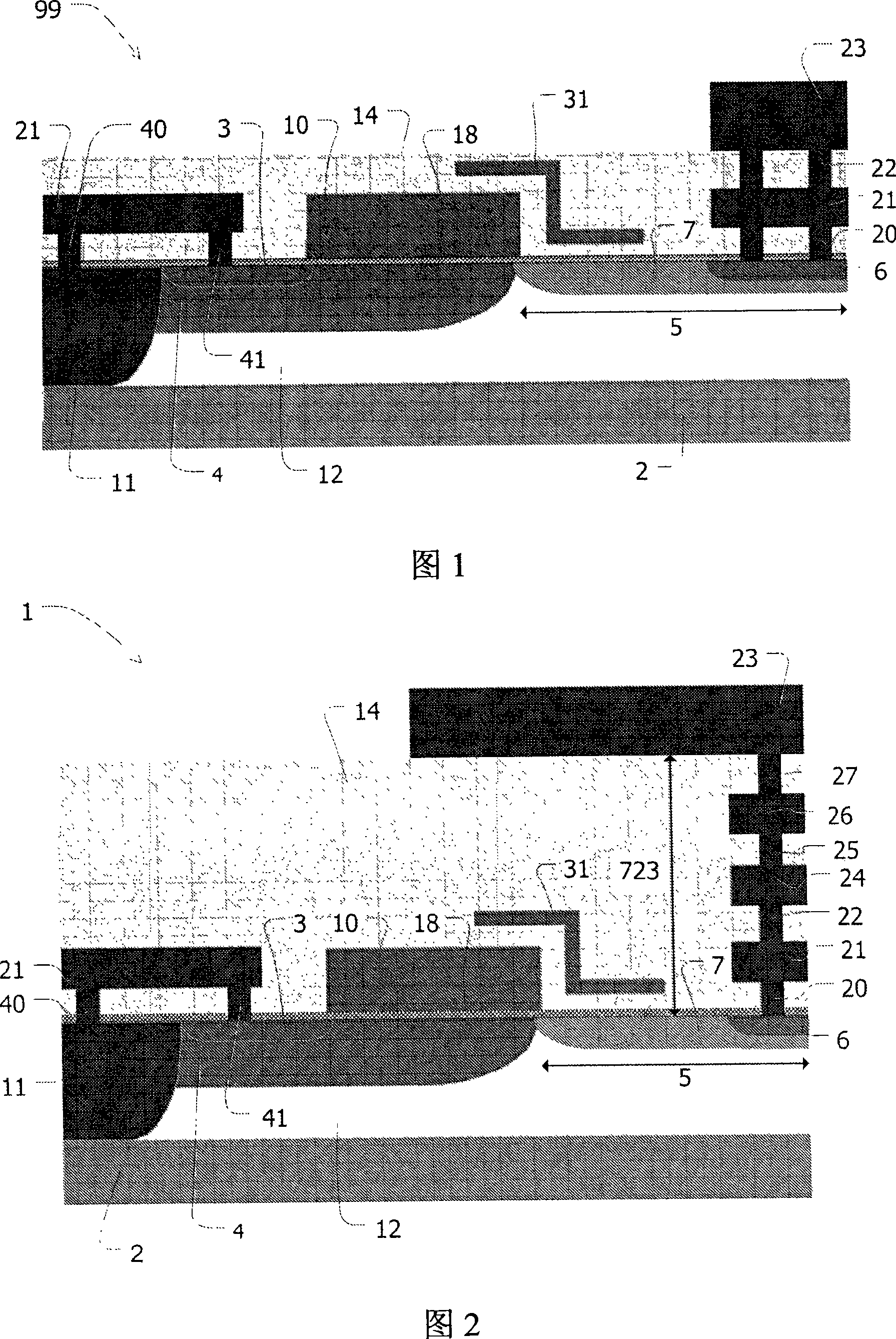

[0021] Figure 1 shows a cross-sectional view of a conventional LDMOS transistor 99 according to the prior art, comprising a substrate 2 of semiconductor material, in this case p-type silicon, on which a p-type epitaxial layer 12 is formed. The LDMOS transistor 99 also includes an n-type source region 3, an n-type drain region 5 and a polysilicon gate electrode 10, which can be equipped with a silicide layer for the polysilicon gate electrode 10 according to the situation and the polysilicon gate electrode 10 is in the channel region 4 Extending above, the polysilicon gate electrode 10 is in this example a laterally diffused p-type region. The source region 3 and the drain region 5 are connected to each other via the channel region 4 . The p-type substrate contact region 11 is electrically connected to the substrate 2 and adjoins the source region 3 on the side opposite to the side adjoining the channel region 4 . The channel region 4 , the substrate contact region 11 , the so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com