A logic unit for oppositional differential power consumption analysis

A technology of differential power analysis and logic unit, which is applied in the direction of instruments, electrical digital data processing, computer security devices, etc., to achieve the effect of avoiding glitches

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

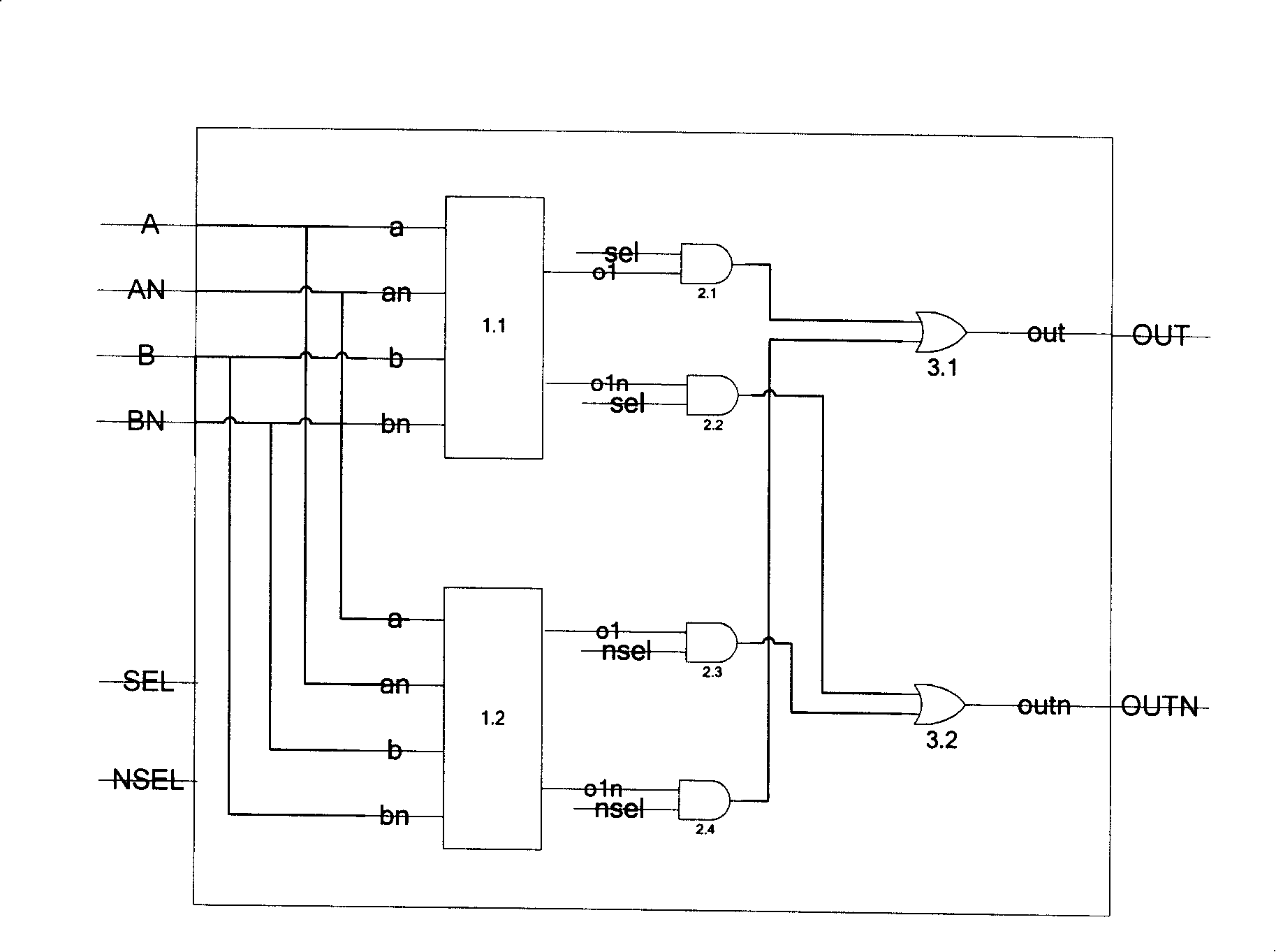

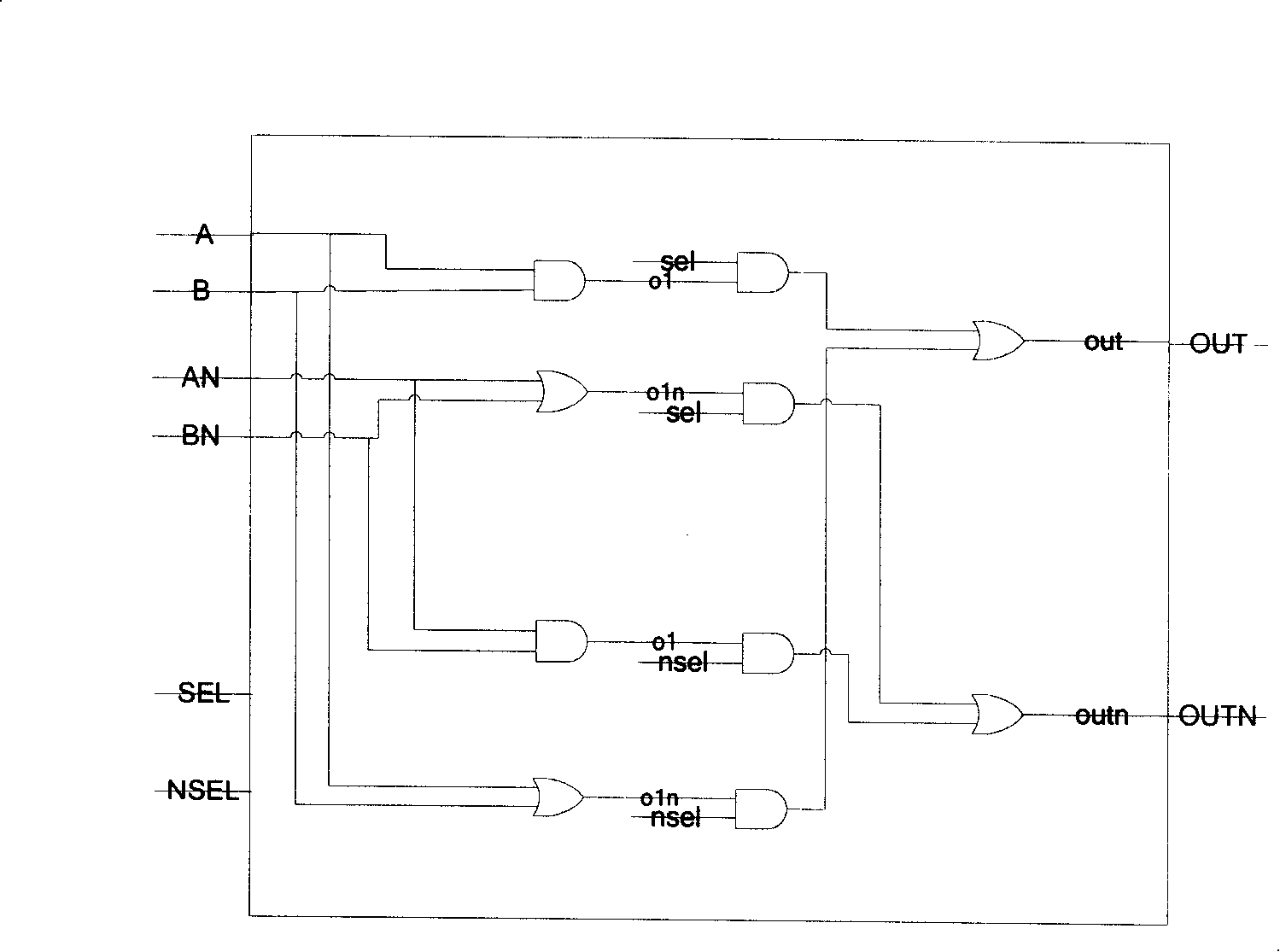

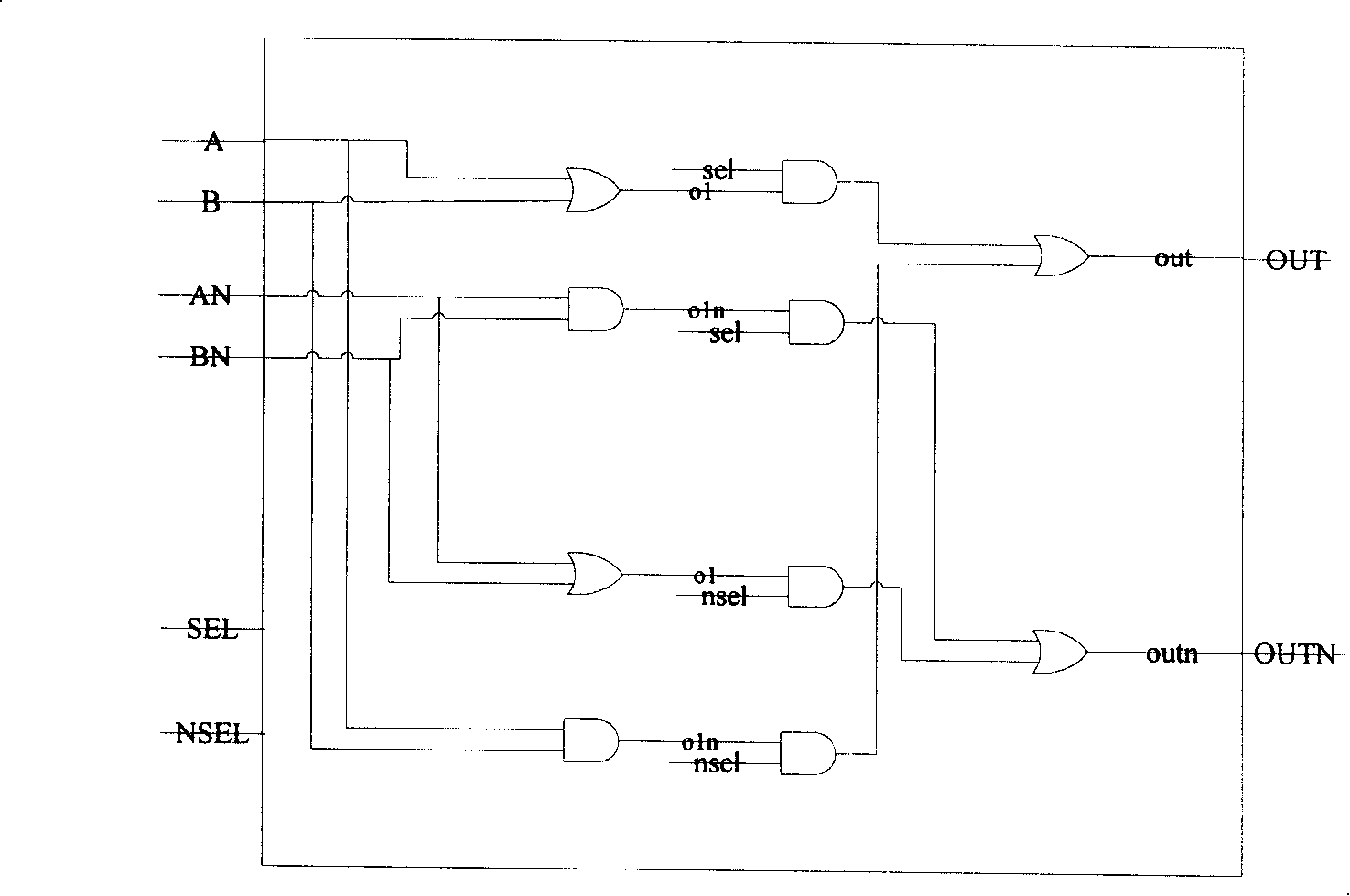

[0015] see figure 1 , the logic unit of the present invention is connected with the input data and the load through the input and output ports. There are two power balance modules in the logic unit, and the inputs of the power balance modules are four original data respectively. The power consumption balance module one 1.1 output is 01 and the random signal sel is connected to the input of the AND gate one 2.1, and the power consumption balance module one 1.1 output is another road 01n and the random signal sel is connected to the input of the AND gate two 2.2. The output of power consumption balance module 2 1.2 is 01 and the random signal nsel is connected to the input of AND gate 3 2.3, and the output of power consumption balance module 2 1.2 is 01n and the random signal nsel is connected to the input of AND gate 4 2.4. The outputs of AND gate 1 2.1 and AND gate 4 2.4 are connected to the output port OUT of the logic unit through OR gate 1 3.1, and the outputs of AND gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com