Non volatile memory device and its operation method

A non-volatile and memory technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problems of complex and time-consuming programming and writing programs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

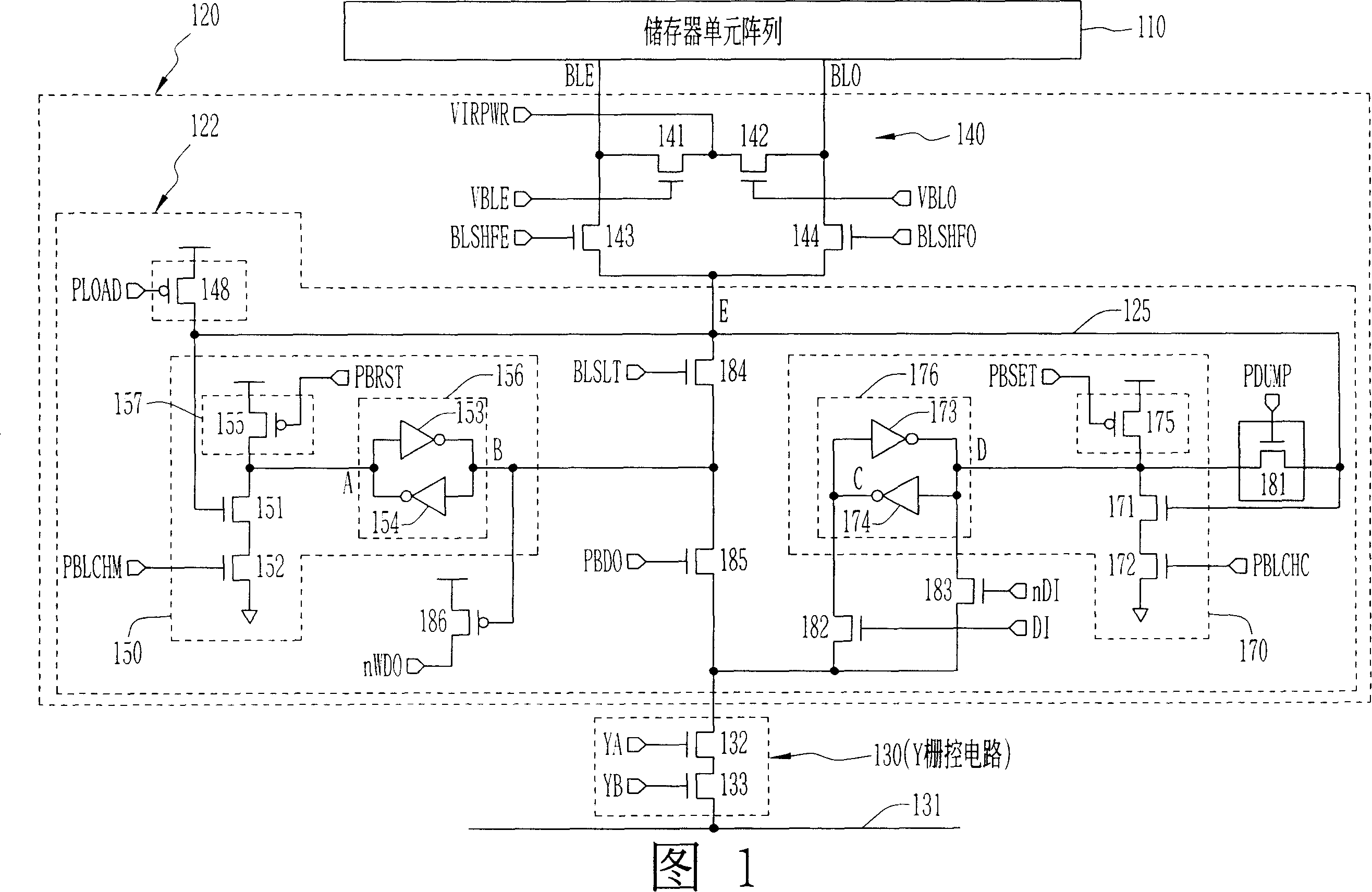

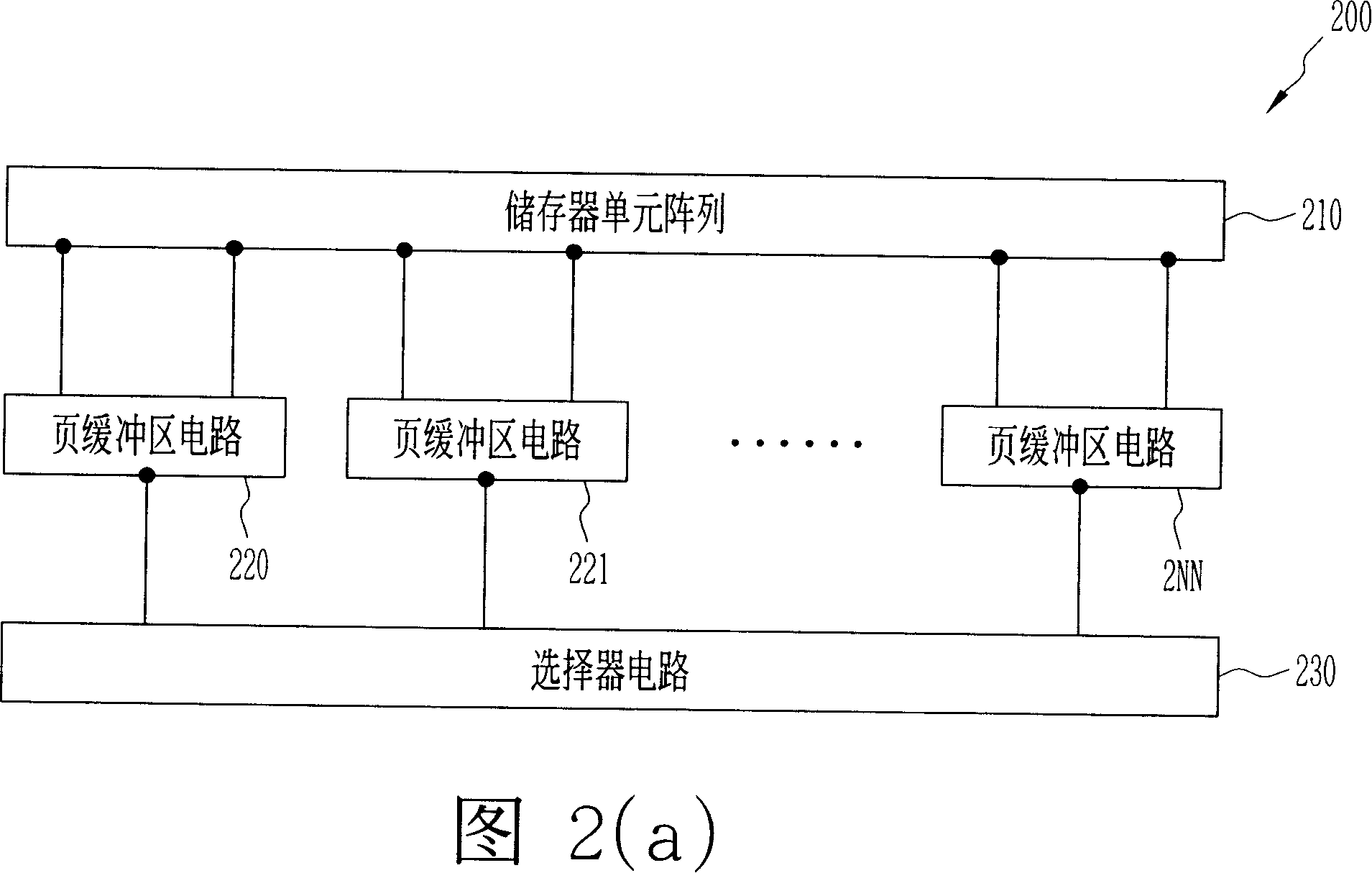

[0037] 2( a ) is a schematic diagram of a flash memory device 200 of the present invention, which includes a memory cell array 210 , a plurality of page buffer circuits 220 , 221 , . . . and 2NN, and a selector circuit 230 . The page buffer circuits 220 , 221 , . . . and 2NN are coupled between the memory cell array 210 and the selector circuit 230 .

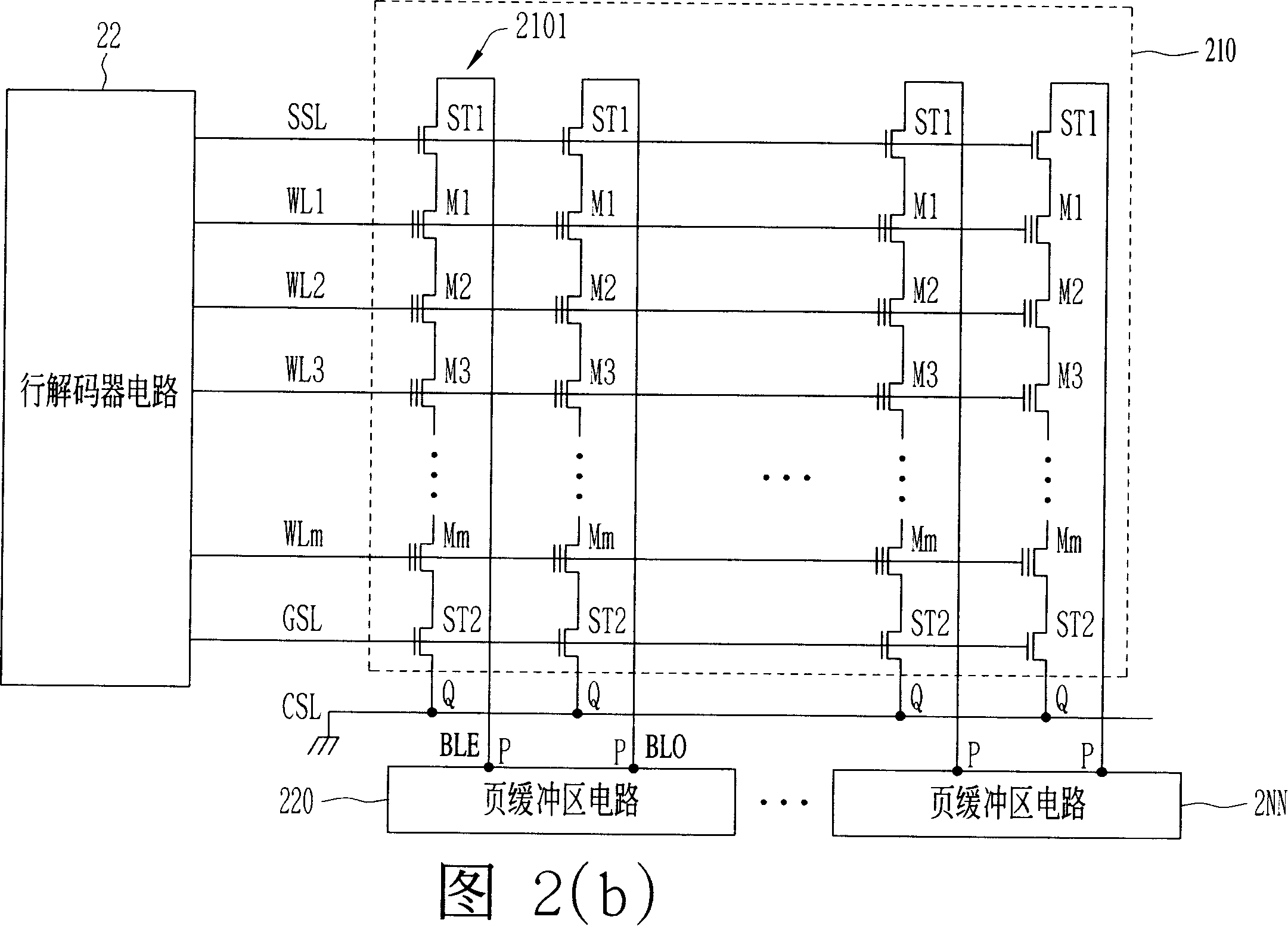

[0038] FIG. 2( b ) is a schematic diagram of the memory cell array 210 according to the first embodiment of the present invention. The memory cell array 210 includes a plurality of cell strings 2101, each of the cell strings 2101 includes a first terminal P and a second terminal Q, and the first terminal P is electrically connected to the corresponding bit line BLE or BLO. The page buffer circuit 220, 221, . . . or 2NN; the second terminal Q is electrically connected to a common source line CSL. The cell string 2101 includes a string selection transistor (string selection transistor) ST1 coupled to the bit line BLE, a ground se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com