A design method and debugging method for mobile phone JTAG debugging interface signals

A debugging interface and design method technology, applied in the direction of telephone communication, sub-office equipment, telephone structure, etc., can solve the problems of design difficulties, safety performance cannot be guaranteed, etc., and meet the needs of convenient application, safe use, and reduced number of signals Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Preferred embodiments of the present invention are described in detail below.

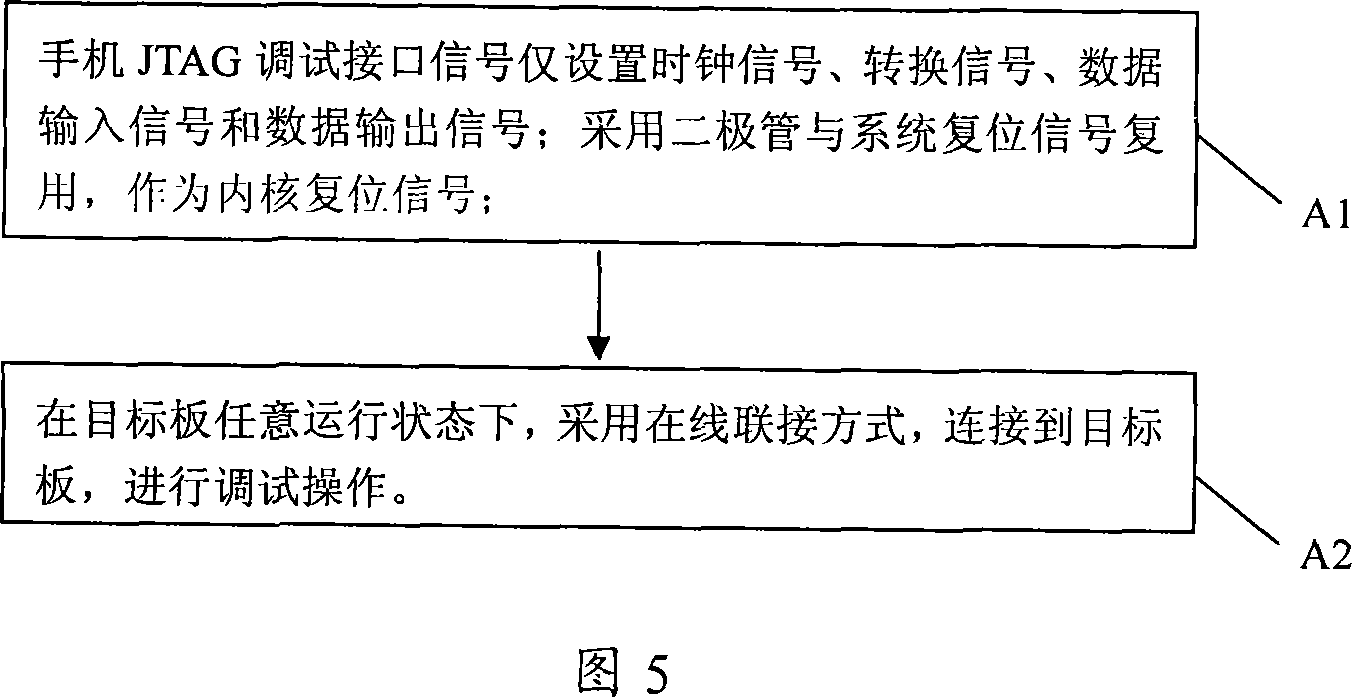

[0031] The invention provides a method for designing a mobile phone JTAG debugging interface signal, wherein: only a clock signal, a conversion signal, a data input signal and a data output signal are set; and a diode is multiplexed with a system reset signal as a core reset signal.

[0032] Specifically, according to the definition of the JTAG protocol (IEEE standard 1149.1), each signal is analyzed as follows:

[0033] 1. JTMS, JTDI, JTDO, JTCK signals are all necessary;

[0034] 2. The JRST signal is used to reset the kernel. In a normal design, the reset signal of the kernel will generally be processed accordingly. This signal is only for when JTAG is connected to the target board, as shown in Figure 4. When the user clicks on the TRACE32 interface When "Target Reset", reset the kernel. Therefore, this signal can be multiplexed with the system reset signal through a diode; under normal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com