Pressure resistant layer structure having dual-medium buried layer and SOI power device using the same

A technology of power devices and dielectric buried layers, which is applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., and can solve problems such as the withstand voltage characteristics of low-k dielectric layer SOI high-voltage devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0047] Embodiment 1: SOI structure with double dielectric buried layer

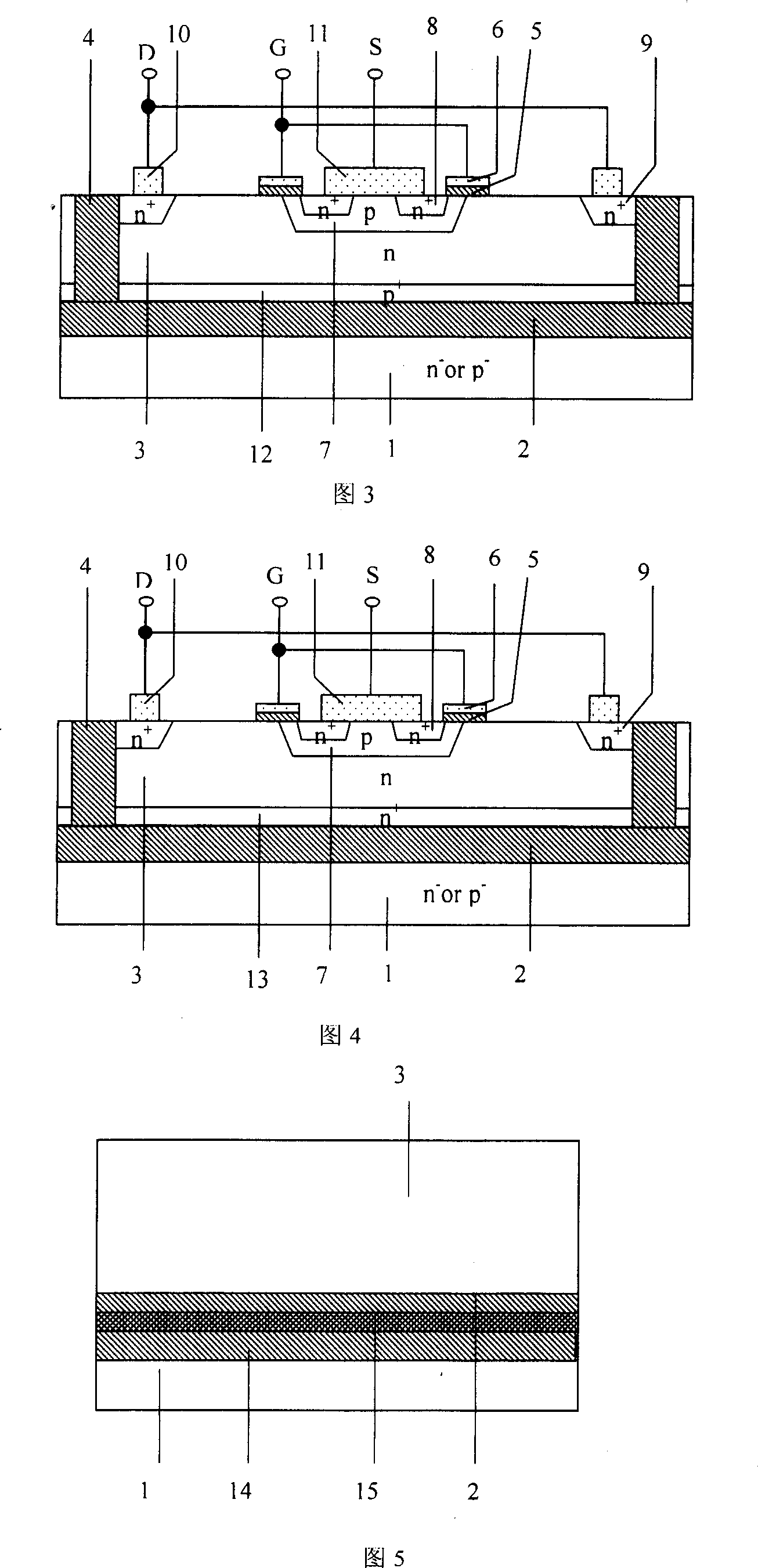

[0048] Fig. 5 is a schematic diagram of the SOI structure with double dielectric buried layers according to the present invention.

[0049] As shown in FIG. 5 , 1 is a substrate layer, 2 is a first dielectric layer (buried layer), 3 is an active semiconductor layer (S layer), 14 is a second dielectric layer (buried layer), and 15 is an intermediate layer. The intermediate layer 15 is located between the first dielectric layer (buried layer) 2 and the second dielectric layer (buried layer) 14, the other side of the first dielectric layer is connected to the active semiconductor layer 3, and the other side of the second dielectric layer 14 is connected to the The substrate layer 1 is connected.

Embodiment 2

[0050] Embodiment 2: SOI LDMOS device structure with double dielectric buried layer

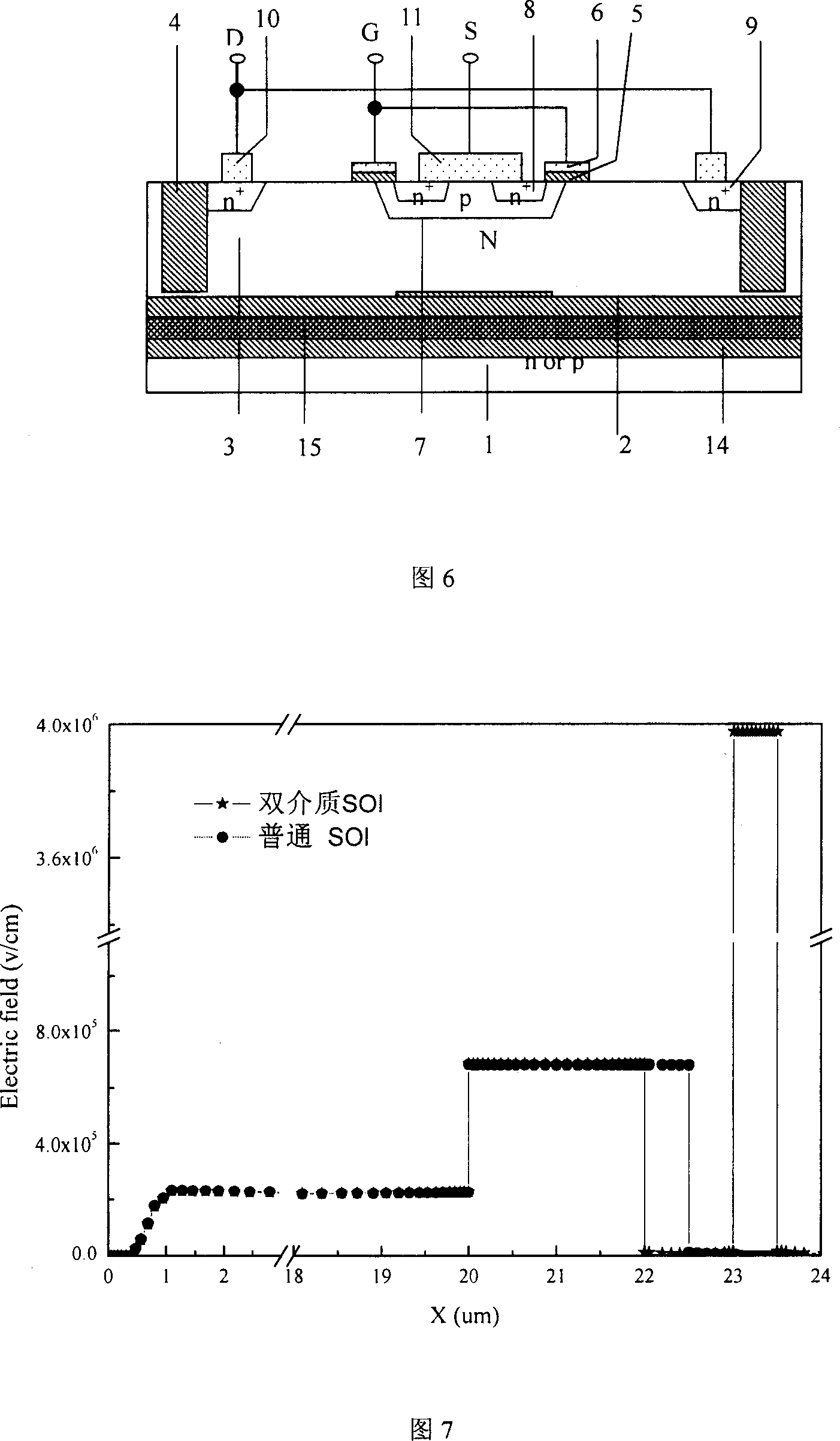

[0051] Fig. 6 is a schematic structural diagram of the SOI LDMOS device with double buried dielectric layers according to the present invention, and Fig. 7 is a vertical electric field distribution diagram of the 8OI LDMOS device with double buried dielectric layers according to the present invention. It can be seen that the electric field on the dielectric layer 14 is much higher than that of the conventional SOI LDMOS dielectric layer. Therefore, under the same thickness of the buried dielectric layer, the withstand voltage of the structure proposed by the present invention is greatly improved. Fig. 8a is a two-dimensional equipotential diagram of a SOI LDMOS device with a conventional structure when it breaks down. Fig. 8b is a two-dimensional equipotential diagram at the time of breakdown of the SOI LDMOS device with double dielectric buried layers according to the present invention. The...

Embodiment 3

[0053] Embodiment 3: SOI IGBT device structure with double dielectric buried layer

[0054] Fig. 9 is a schematic diagram of the SOI IGBT device structure with double dielectric buried layers according to the present invention. As shown in Figure 9, 1 is the substrate layer, 2 is the first dielectric layer, 3 is the active semiconductor layer (S layer), 6 is the gate electrode, 7 is the p (or n) well, and 8 is the n + (or p + ) cathode area, 9 is n + (or p + ) anode region, 14 is the second dielectric layer (buried layer), 15 is the intermediate layer, 17 is the anode, 18 is the cathode, and 19 is the p (or n) well. The intermediate layer 15 is located between the first dielectric layer (buried layer) 2 and the second dielectric layer (buried layer) 14, the other side of the first dielectric layer is connected to the active semiconductor layer 3, and the other side of the second dielectric layer 14 is connected to the The substrate layer 1 is connected.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com