Construction method of multi-code rate compatible LDPC code and its decoder

A technology of LDPC codes and construction methods, applied in the information field, can solve problems such as increased algorithm complexity, increased construction algorithm complexity, and increased difficulty in low code rate H matrix construction, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

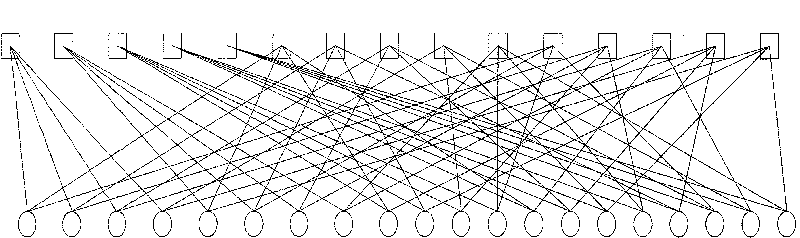

[0103] Below through embodiment, further illustrate the present invention in conjunction with accompanying drawing, but do not limit the scope of the present invention in any way. Embodiment 1: Construct fixed-length irregular multi-code rate permutation matrix LDPC code

[0104] The following specific description utilizes the construction method of the present invention to construct a code length of 8064 bits, and the code rate is 7 / 8, 3 / 4, the process of the multi-code rate LDPC system code of 1 / 2:

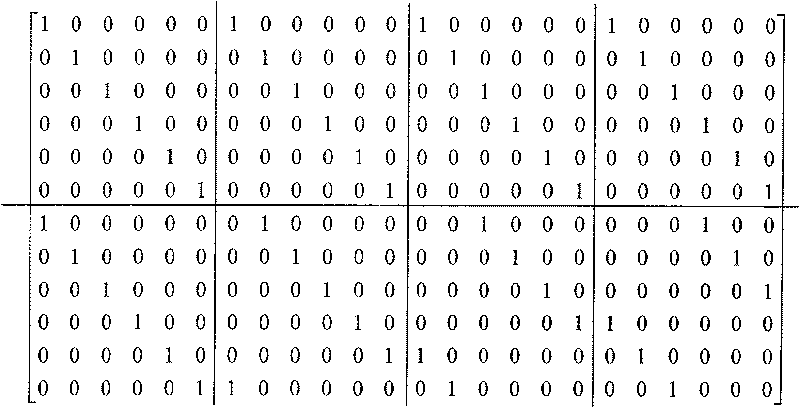

[0105] Step 1, determine the parameters of the H matrix. Known code length N=8064, then check equation number M=1008 when code rate is 7 / 8, check equation number M=2016 when code rate is 3 / 4, check equation number when code rate is 1 / 2 is 4032, the size of the H matrix is 1008×8064, 2016×8064, 4032×8064 respectively. Find the factors of M and N respectively, we can get N=112×72, M 1 =112×9, M 2 =112×18, M 3 =112×36, so we can choose the size of each sub-block to be 112×11...

Embodiment 2

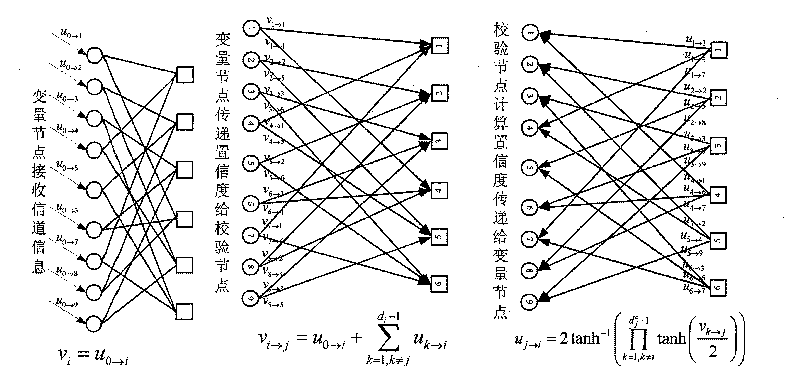

[0135] Embodiment 2: Decoder

[0136] The overall structure of the decoder is as follows Figure 15 As shown, it can be divided into four parts: Controller (control module), Memory (memory), VNU (variable node computing unit) and CNU (check node computing unit).

[0137] Among them, a total of 72 variable node calculation units are required, and a total of 45 check node calculation units are required. The decoding algorithm can use a simplified algorithm of the sum-product algorithm—the minimum sum algorithm. Since there are 279 non-zero permutation matrices of the H matrix with a code rate of 7 / 8 in the constructed multi-code rate H matrix, the H matrices of other code rates are all split from this matrix, so the multi-code rate decoder A codeword with a decoding rate of 7 / 8 requires a total of 279 dual-port RAMs with a size of 112×7bits (here, the quantization width is 7). When the code rate is other values, the decoder multiplexes these 279 dual-port RAMs. , they serve as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com