Delay locked loop circuit and method for provding delay locked loop clock of synchronous memory device

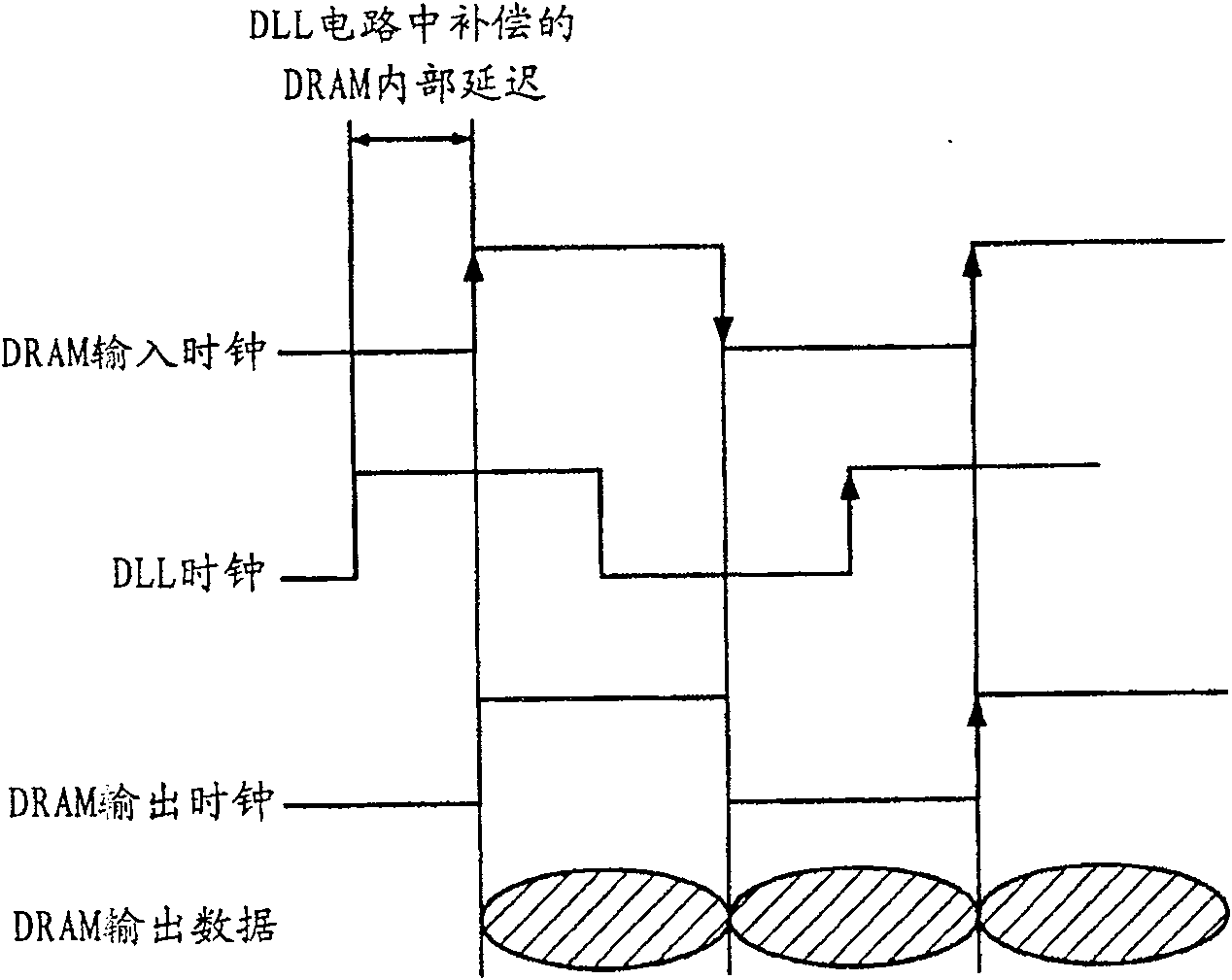

A delay-locked loop and memory technology, applied in the field of DLL circuits, can solve the problems of difficult data transmission and different phases.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

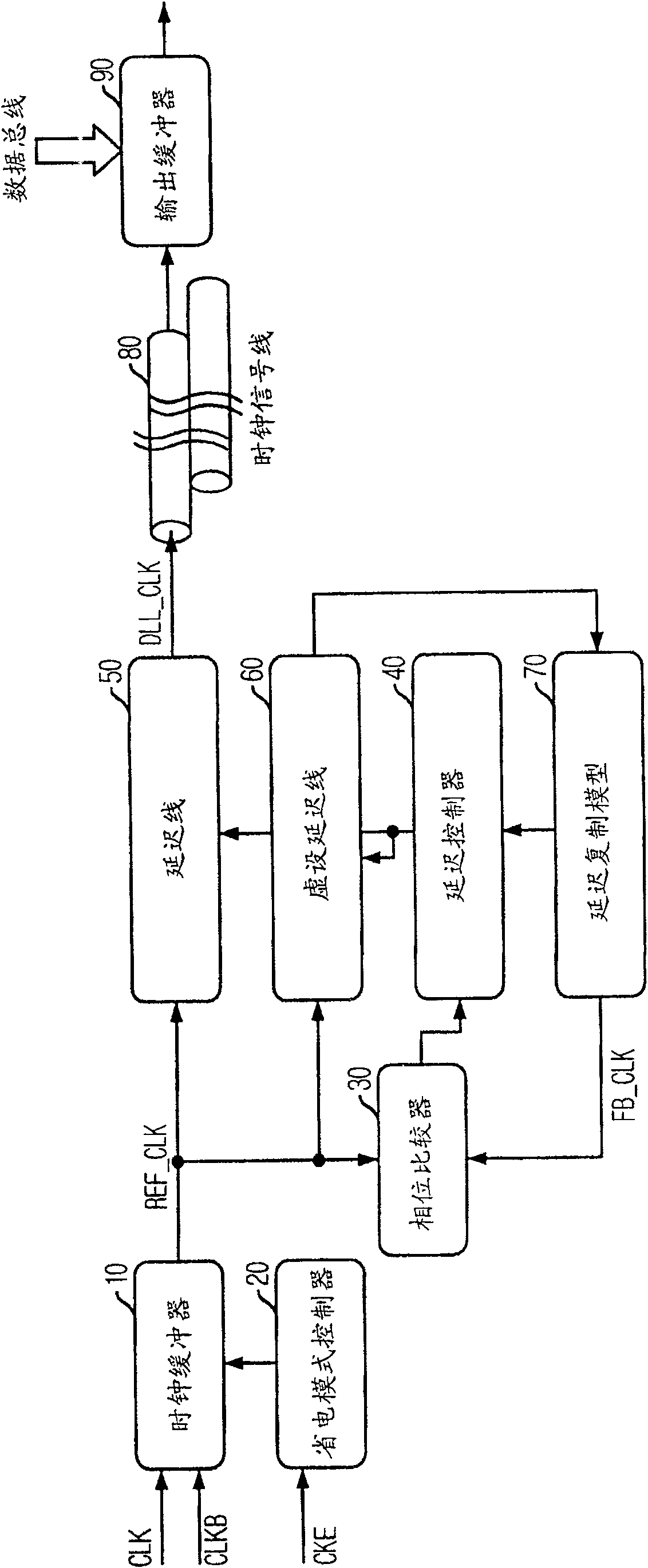

[0052] A delay locked loop (DLL) circuit according to an exemplary embodiment of the present invention will be described in detail with reference to the accompanying drawings.

[0053] Figure 4 is a block diagram of a DLL circuit according to an embodiment of the present invention.

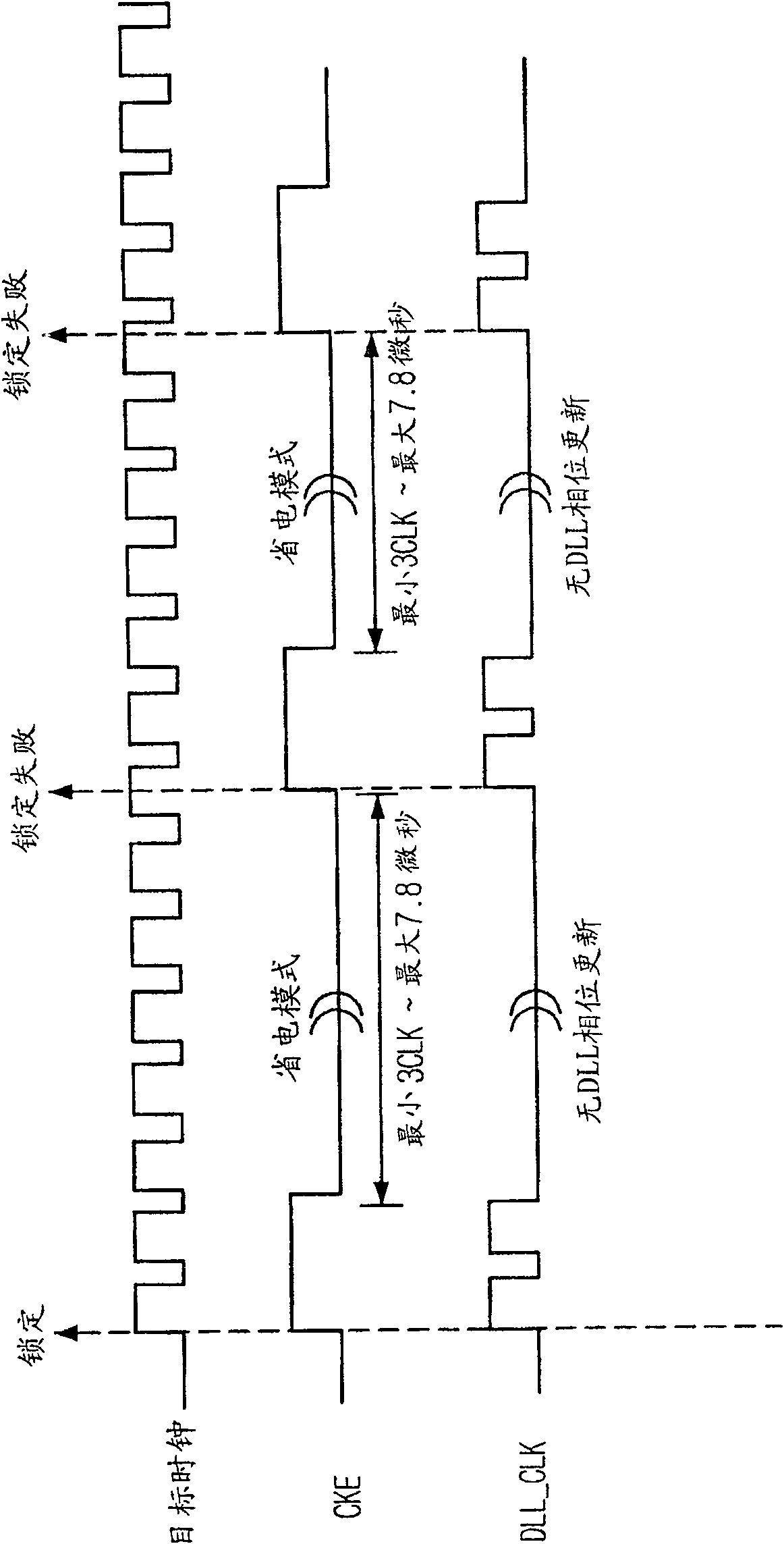

[0054] The DLL circuit 600 includes a power saving mode controller 100 , a first clock buffer 200 and a second clock buffer 300 , a clock selection unit 400 and a phase update unit 500 .

[0055] The power saving mode controller 100 generates a power saving mode control signal CTRL which determines initiation or termination of the power saving mode in response to the clock enable signal CKE.

[0056] The first clock buffer 200 receives and buffers the external clock signal CLK and the external clock bar signal CLKB in response to the power saving mode control signal CTRL, thereby outputting the buffered signal as the first internal clock signal ICLK_NM. .

[0057] The second clock buffer 300 r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com