Network-on-chip digital router and its parallel data transmission method

A network-on-chip and router technology, which is applied in the field of network-on-chip digital routers and their parallel data transmission, can solve the problems of not being able to give full play to the functional advantages of the system chip, increasing chip area consumption, and intensified bus resource competition, so as to solve the problem of resource occupation and Data congestion problem, solving the problem of intensified competition, and reducing the effect of data congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

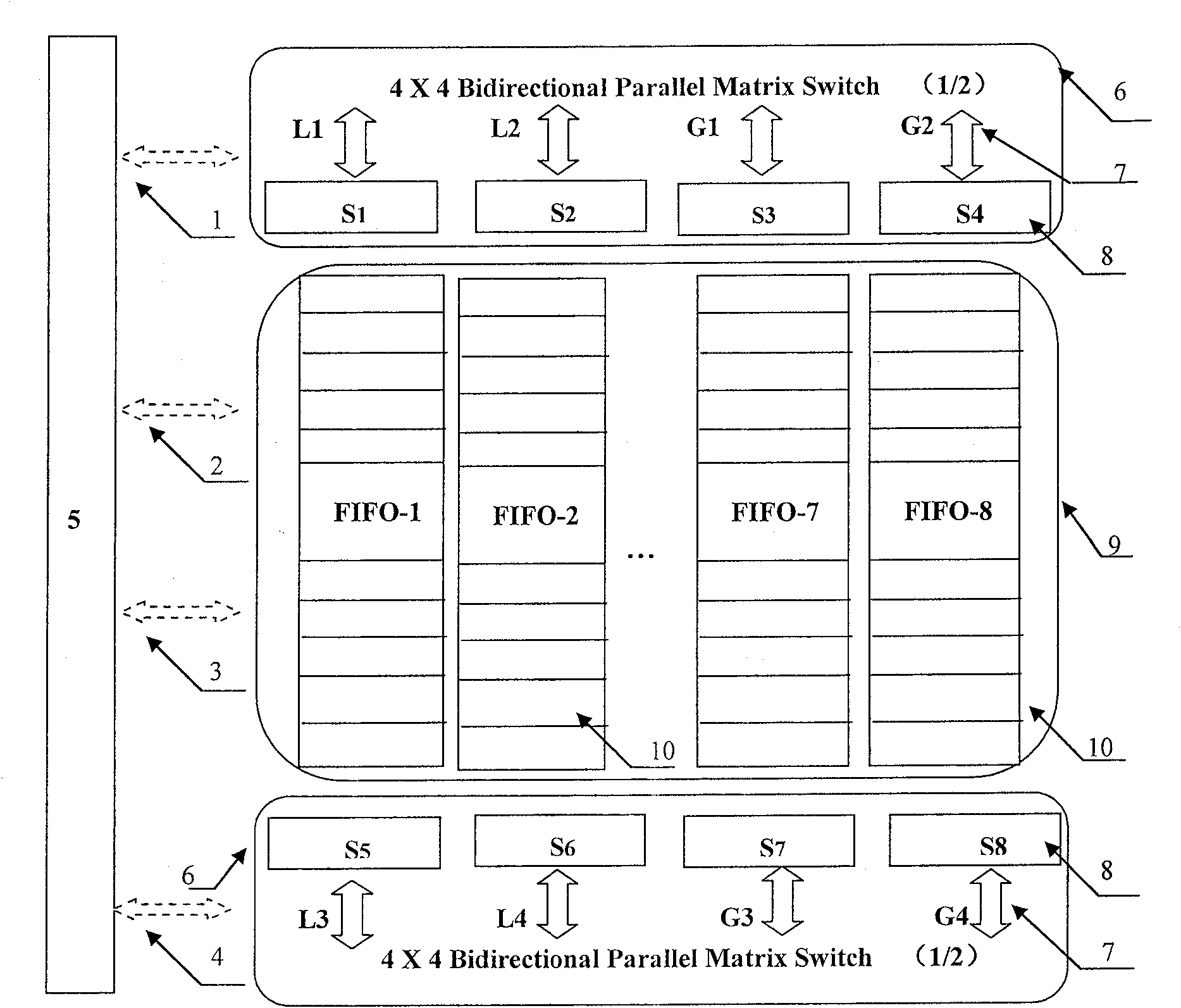

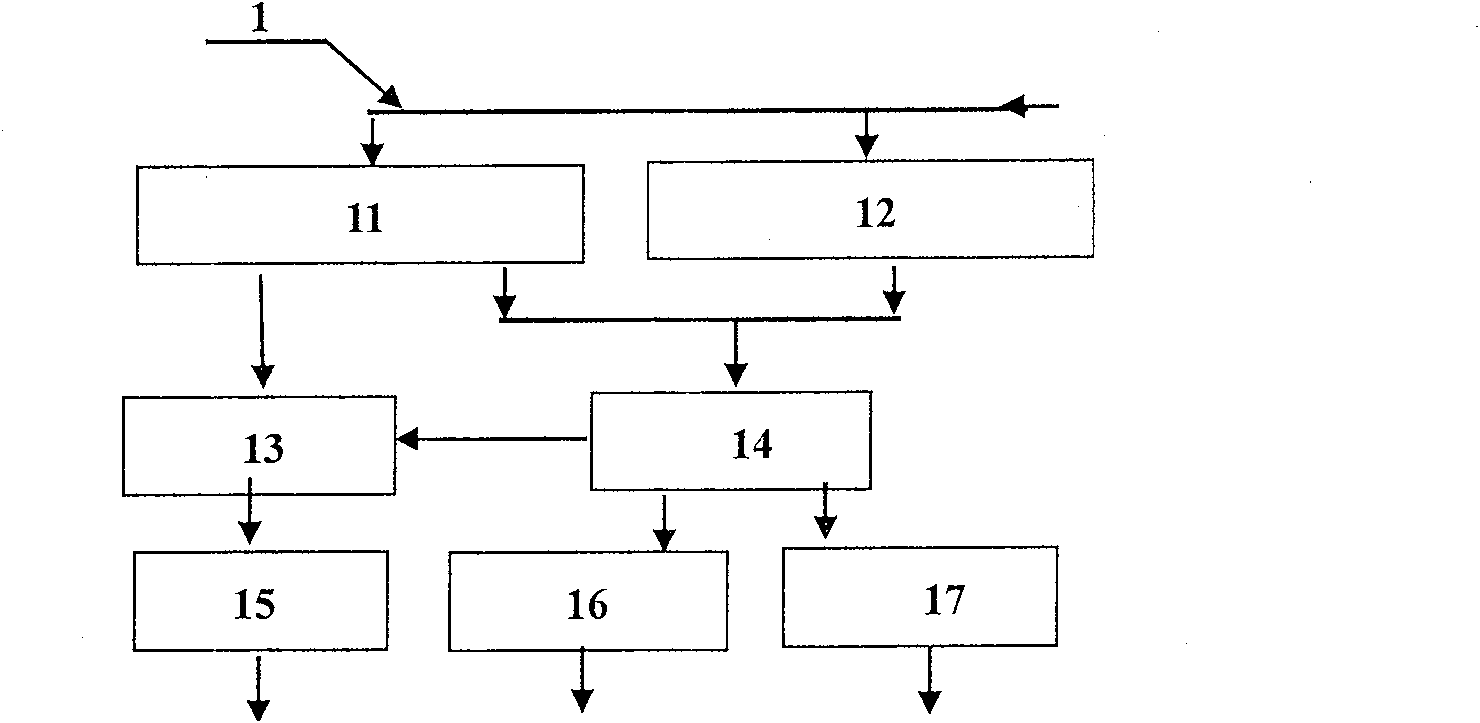

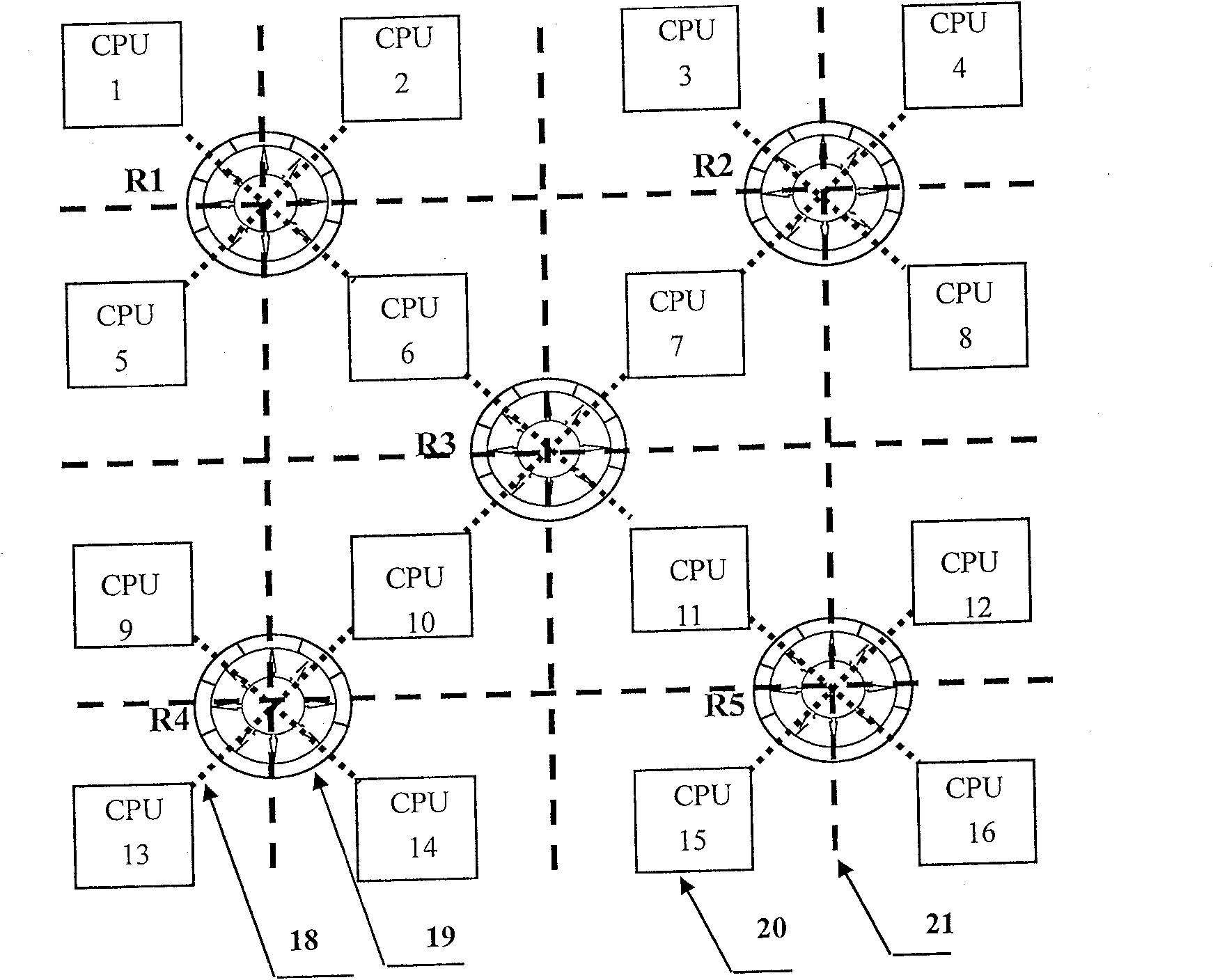

[0034] The embodiment of the router of the present invention is for example Figure 1-3 As shown, it is composed of FIFO shift buffer 10, two groups of synchronous matrix switch arrays 8, data routing decision-making module 5, The parallel network interface 7 is collected, and the input port of the parallel network interface 7 is connected with the synchronous matrix switch array 8; the output interface of the synchronous matrix switch array 8 on one side of the memory and the input interface of all first-in-first-out wave shift buffers 10 on the chip Connect to each other, the output interfaces of all the first-in-first-out wave shift buffers 10 on the chip are connected to the synchronous matrix switch array on the other side, and are connected to the parallel network interface 7 through the synchronous matrix switch array; the data routing decision module 5 includes a data stream header register 11 and Status flag register 12, its interface contains command output interface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com