Method and apparatus for testing integrated circuits

A test module and test system technology, applied in digital circuit testing, electronic circuit testing, etc., can solve problems such as impossible plug and play, and achieve the effects of reducing test costs, reducing work intensity, and accelerating turnaround time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

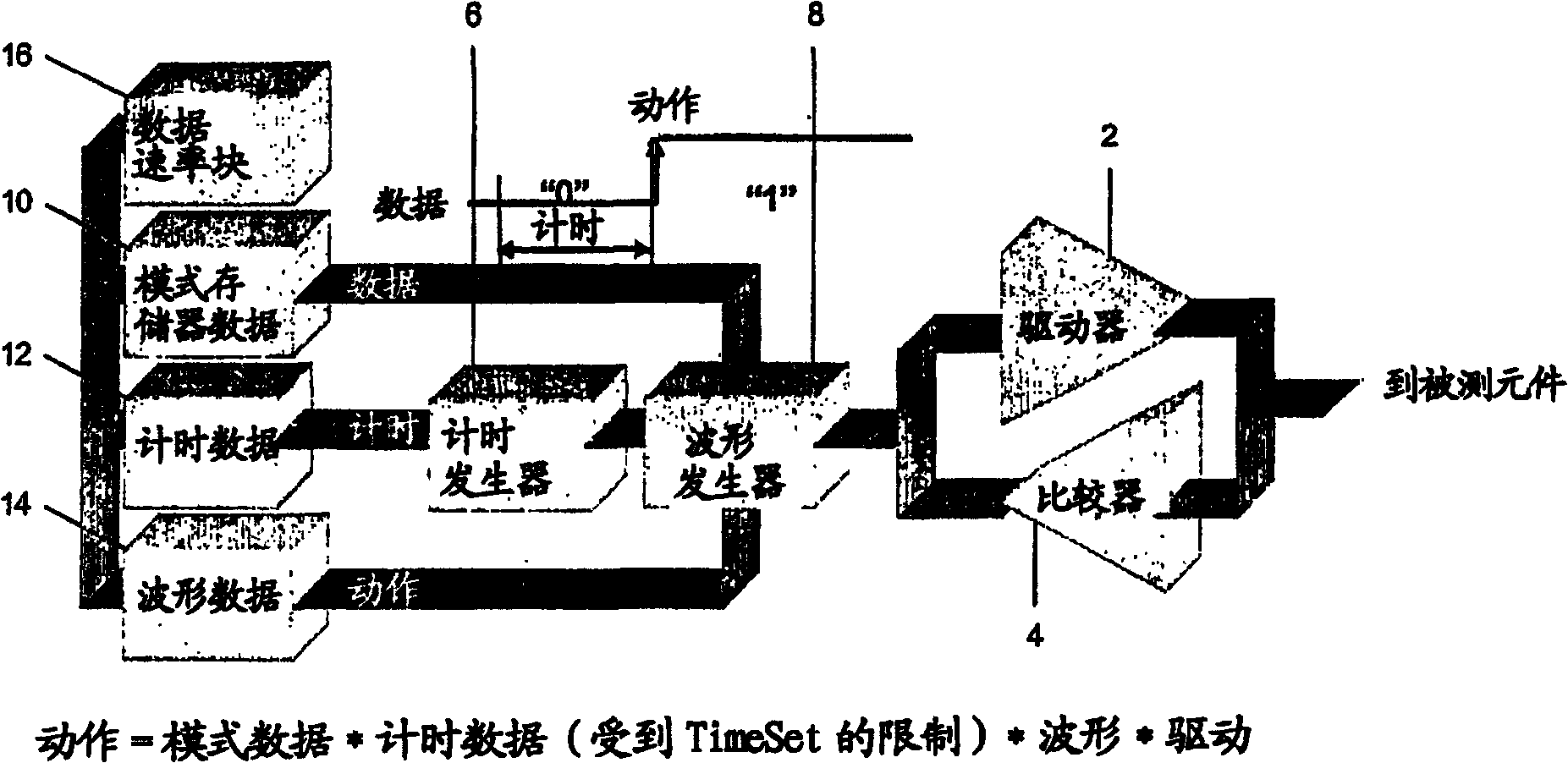

[0034] figure 1 Shown is the general architecture of the conventional tester, showing how the signal is generated and applied to the device under test (DUT). Each DUT input pin is connected to the driver 2 of the application test data, and each DUT output pin is connected to the comparator 4 (comparator). In most cases, tri-state driver-comparators are used, so that each test pin (channel) can be used as both an input pin and an output pin. The collection of test pins used for a single DUT forms a test site, which is associated with a timing generator 6 (timing generator), a waveform generator 8 (waveform generator), and a pattern memory 10 (pattern memory). A timing data memory 12 (timing data memory), a waveform memory data 14 (waveform memory data) and a block 16 (block) defining a data rate (data rate) work together.

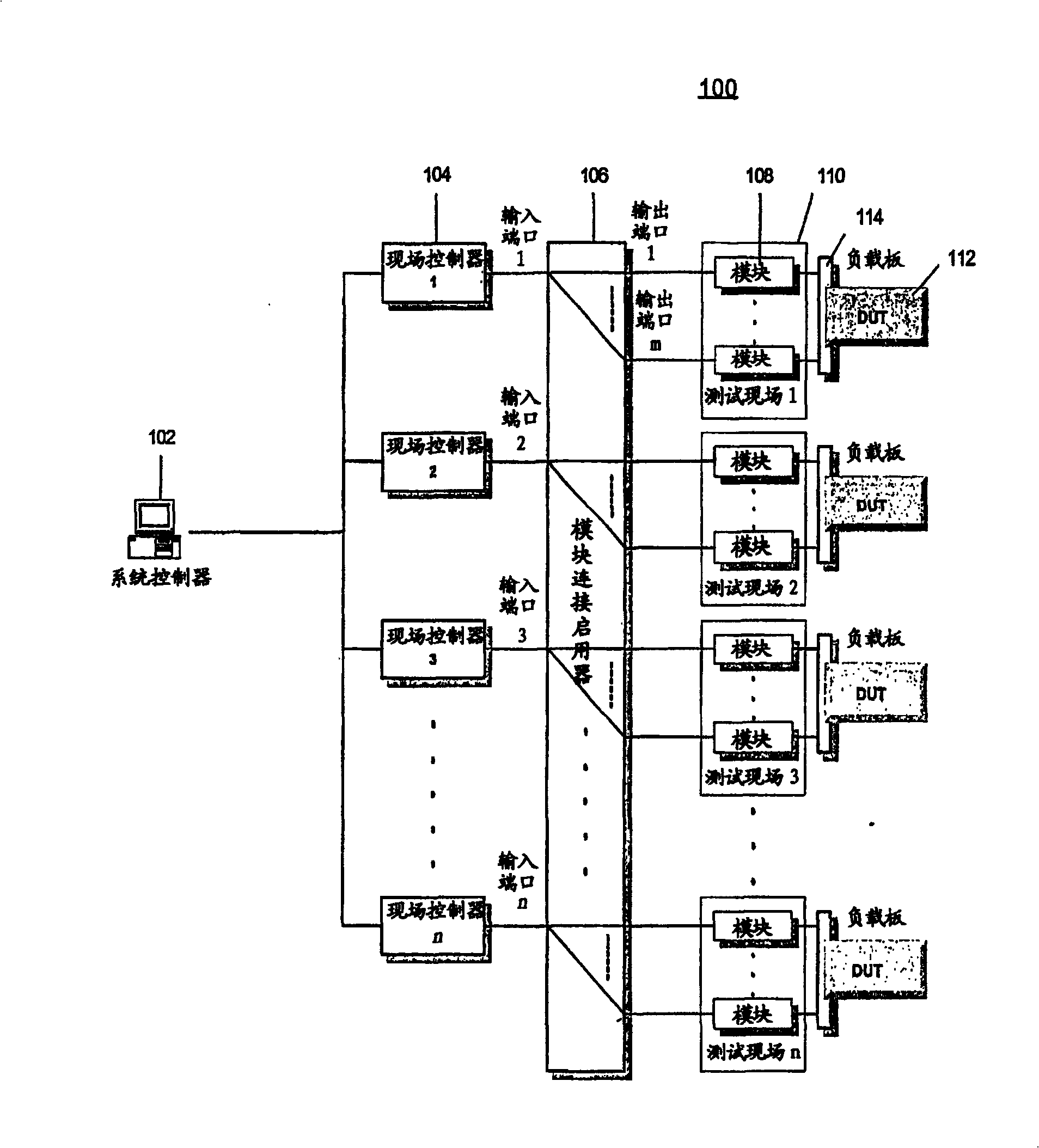

[0035] figure 2 Shown is a system architecture 100 according to an embodiment of the invention. The system controller (SysC) 102 is coupled to a plurality o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com