Software and hardware synergistic simulation/ validation system and vector mode simulation/ validation method

A technology for software and hardware collaboration and verification methods, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of reduced efficiency, increased complexity, and increased difficulty of SoC systems, reducing workload and improving simulation. Effects of speed, improved accuracy and correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

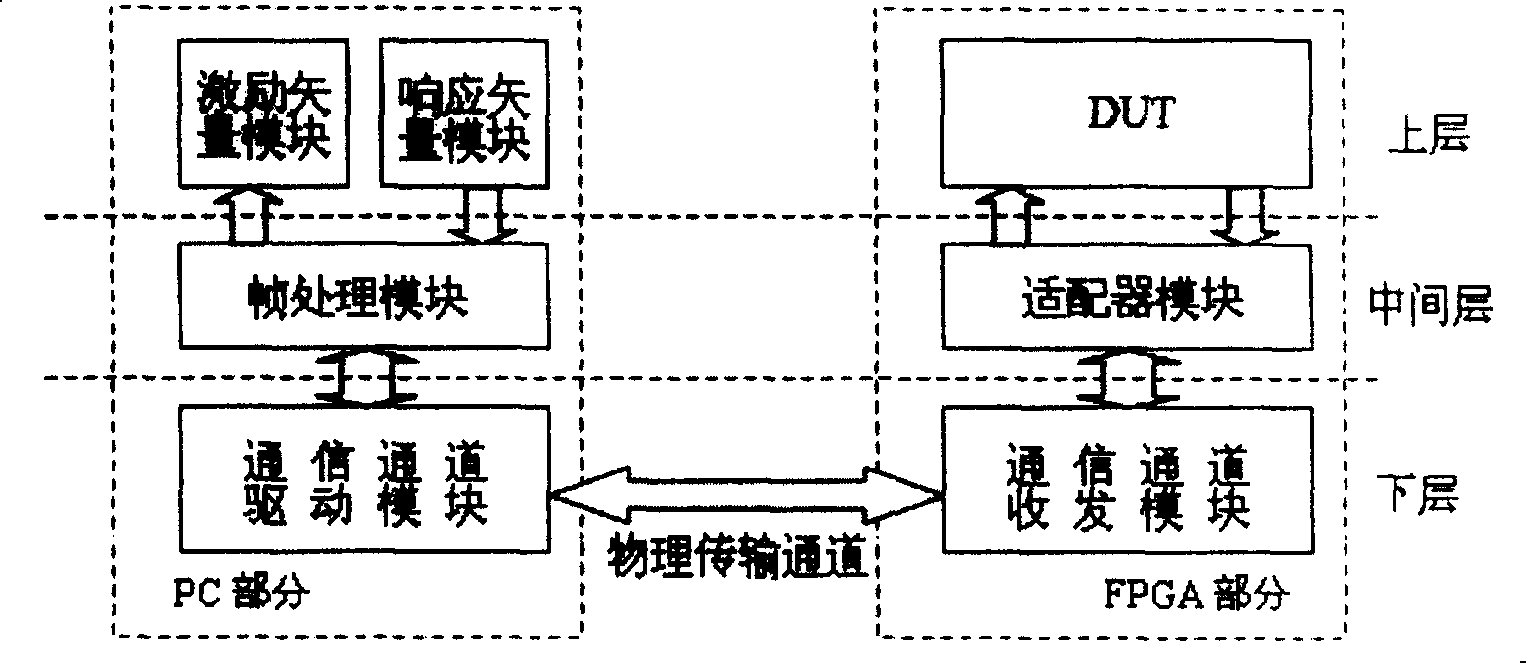

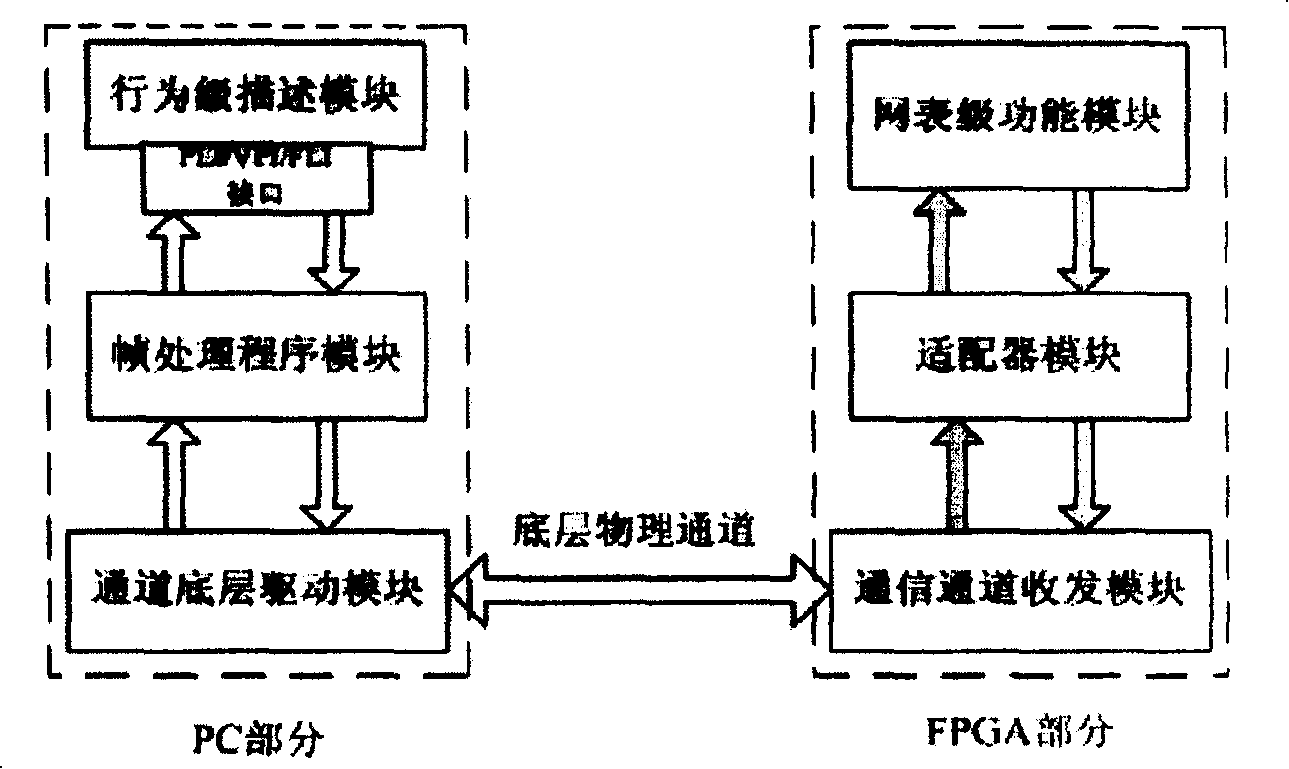

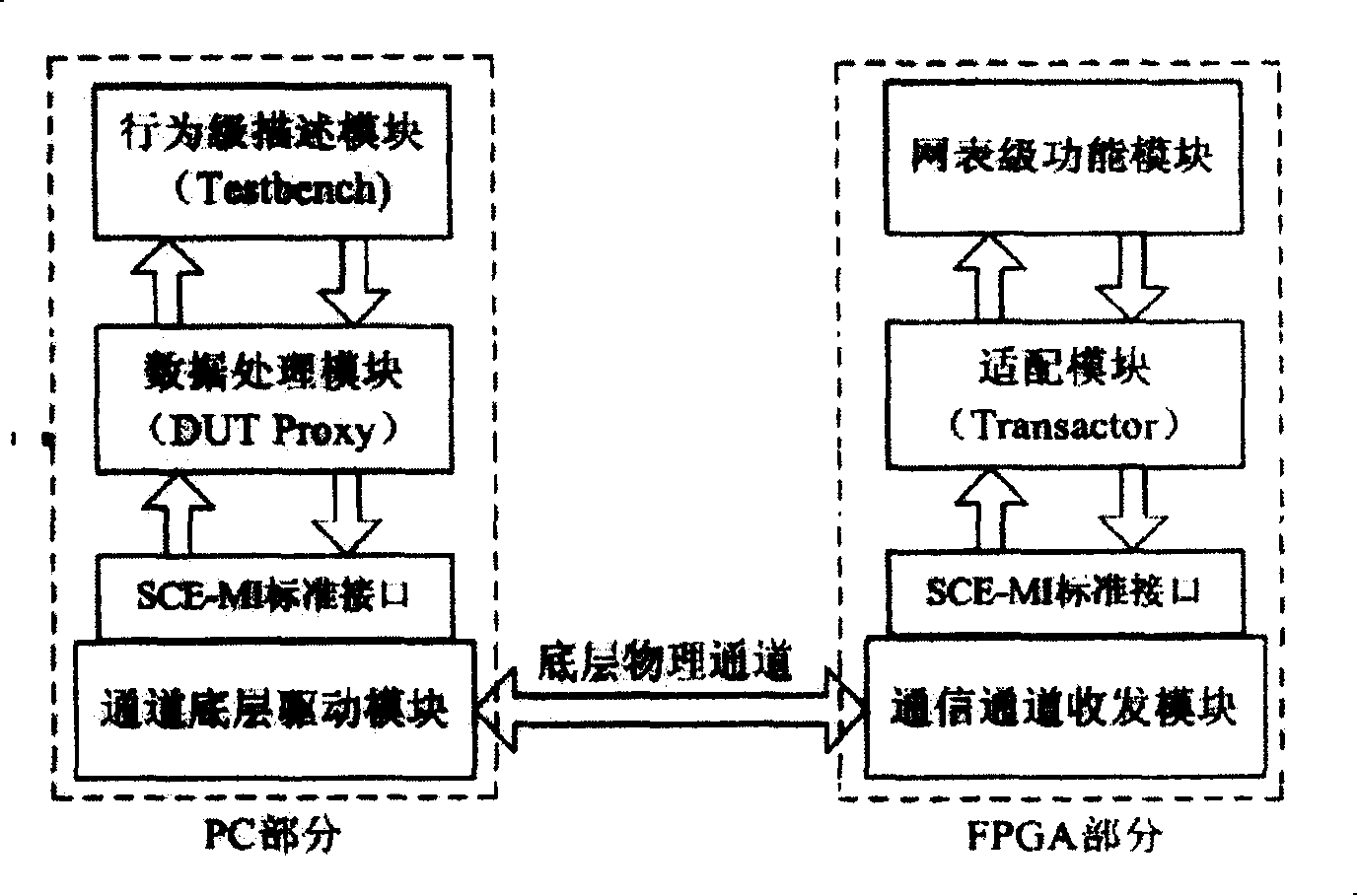

[0068] According to the modular analysis of the above-mentioned architecture, the realization of the improved Vector mode software-hardware co-simulation can be completed by realizing the functions of each module separately, and then connecting them according to the specified interface and combining them into a whole. The specific realization can be Divided into the following sections:

[0069] 1. Software part:

[0070](1) Use text format, and describe the stimulus vector file and response vector file in accordance with the specified format;

[0071] (2) adopt C / C++ to realize the frame processing module of the software part;

[0072] (3) Realize the communication channel driver module by calling the API function related to the operating system.

[0073] Second, the hardware part:

[0074] (1) The communication channel transceiver module in the FPGA hardware platform part can be realized through a dedicated interface chip and the internal logic function of the FPGA, and co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com