Memory cell array biasing method and a semiconductor memory device

a memory cell array and biasing technology, applied in the direction of girders, instruments, joists, etc., can solve the problems of limited number of unit cells connected to the word line wlb>0/b>, wlb>1/b>, and it is difficult to increase perform stable sensing. , to achieve the effect of stable sensing and increasing the operating speed of the semiconductor memory devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033]The present invention will now be described more fully with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. Like reference numerals represent like elements throughout the drawings.

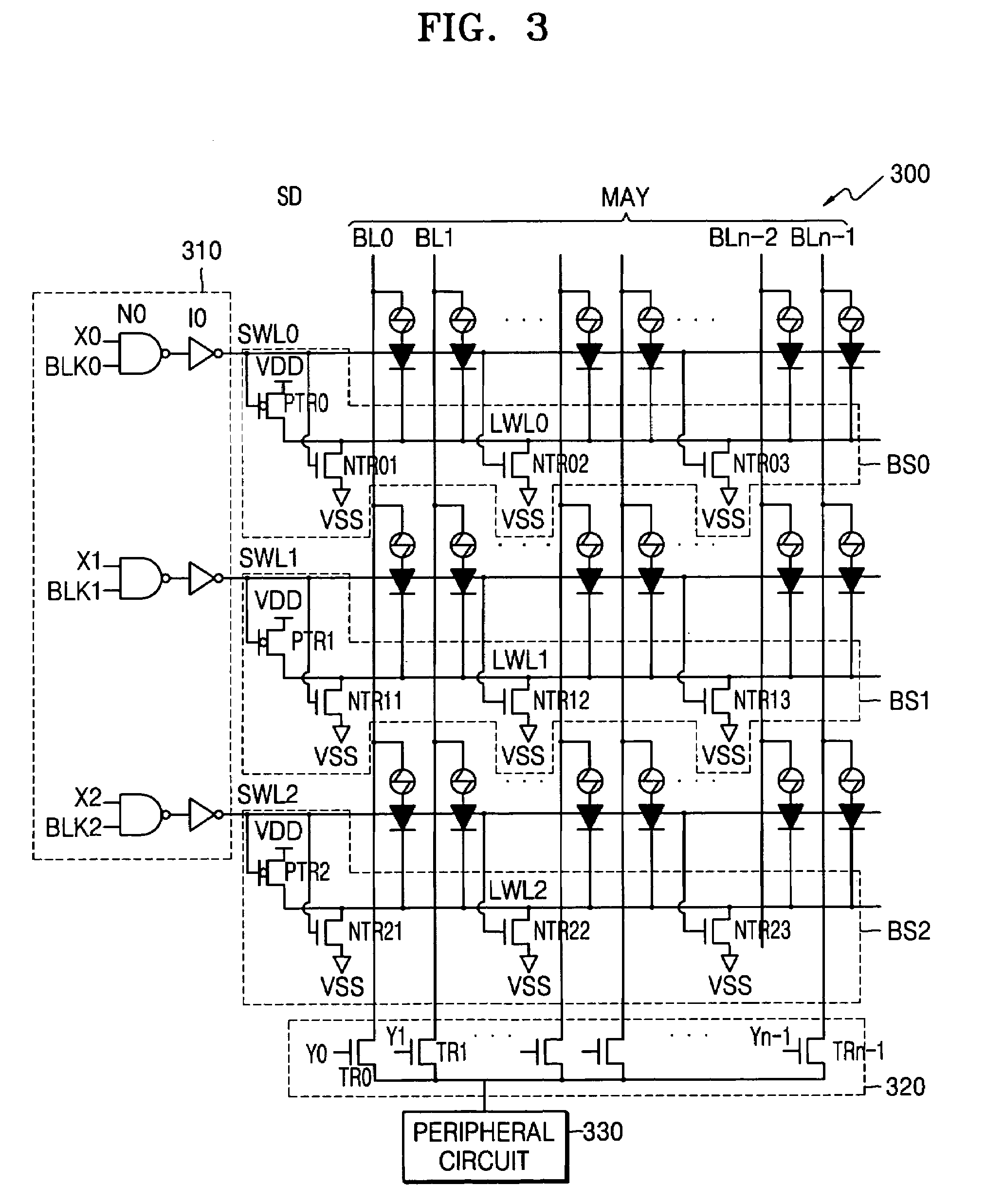

[0034]FIG. 3 illustrates a semiconductor memory device 300 according to an embodiment of the present invention. Referring to FIG. 3, the semiconductor memory device 300 includes a memory cell array MAY, bias circuits BS0, BS1, and BS2, and a word line driver 310. The semiconductor memory device 300 is a PRAM, which includes a memory cell having a phase change material, e.g., GST, connected to a first line, and a diode connected between the phase change material and a second line. The PRAM may be similar to or the same as that shown in FIG. 1.

[0035]As shown in FIG. 3, the semiconductor memory device 300 is connected to a peripheral circuit 330 and a column decoder 320. The peripheral circuit 330 may comprise a write driver (not shown) and a sense ampl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com