Entering and exiting power managed states without disrupting accelerated graphics port transactions

a technology of power management and power state, applied in the field of computer systems, can solve the problems of affecting the efficiency of the system, loss or corruption of any requests remaining in queue, and loss of any untransferred data, etc., and achieve the effect of reducing power consumption, and reducing the number of requests

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

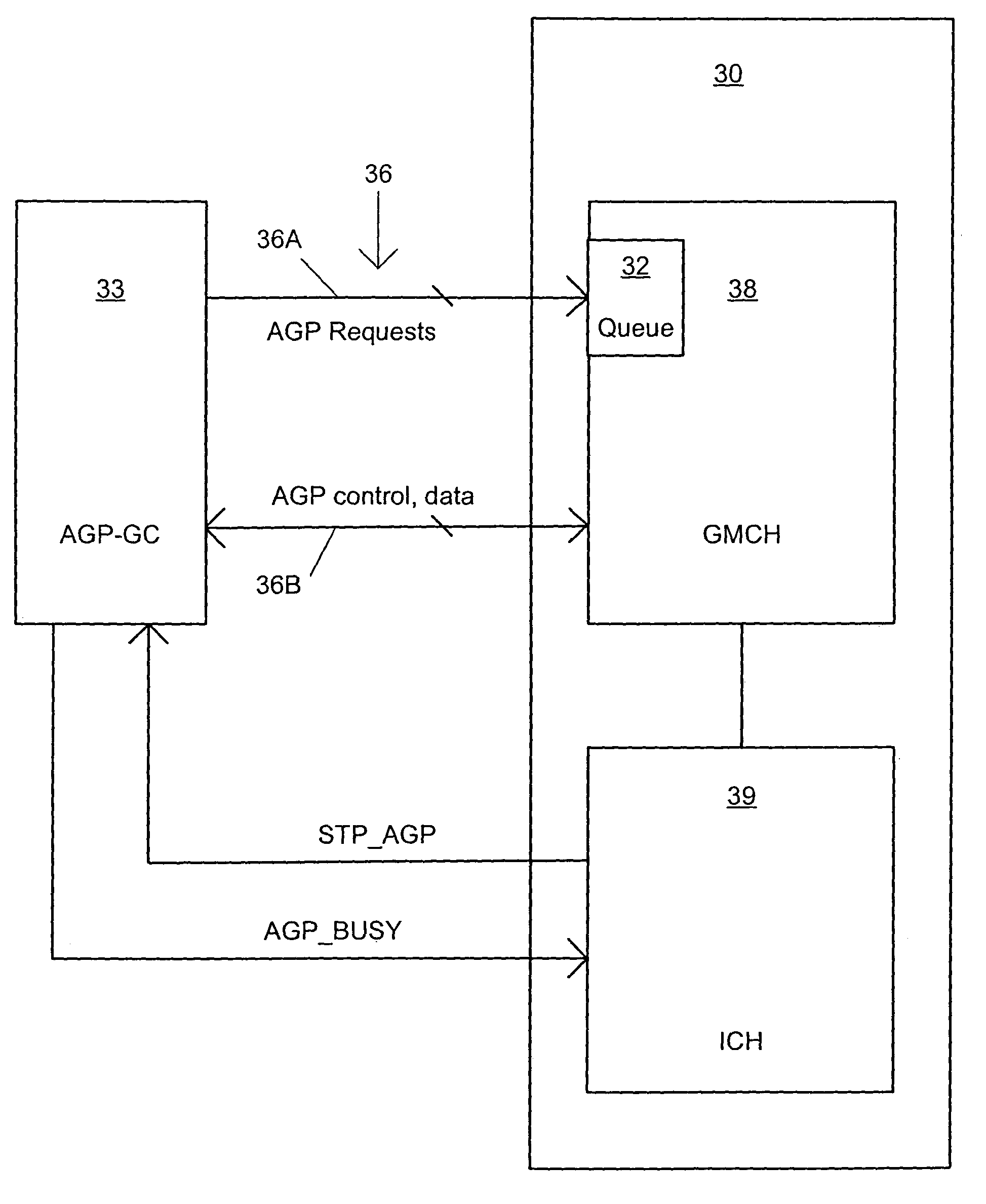

[0014]The invention provides the capability for a graphics controller interface, referred to herein as an AGP-GC, to signal whether it is busy, i.e., whether it has made any uncompleted requests, so that the core controller can delay entering a low power state until the AGP-GC has completed any pending requests. As will be seen, this capability can also be used to initiate an exit from a sleeping state when the AGP-GC has a request to make during a low power state. The invention also provides the capability for the core controller to signal the AGP-GC of an intended entry into a low power state so that the AGP-GC can cease issuing requests to the core controller.

[0015]The invention can be implemented with a pair of signals, one from the core controller to notify the AGP-GC of an intent to enter a low power state, and the second from the AGP-GC to notify the core controller whether the AGP-GC has an uncompleted request pending.

[0016]FIG. 3 shows a portion of a system incorporating th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com