Layer member forming method

a technology of layer member and forming method, which is applied in the direction of coating, coating, chemical vapor deposition coating, etc., to achieve the effect of easy forming to desired thickness in a short time, no damage, and short tim

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

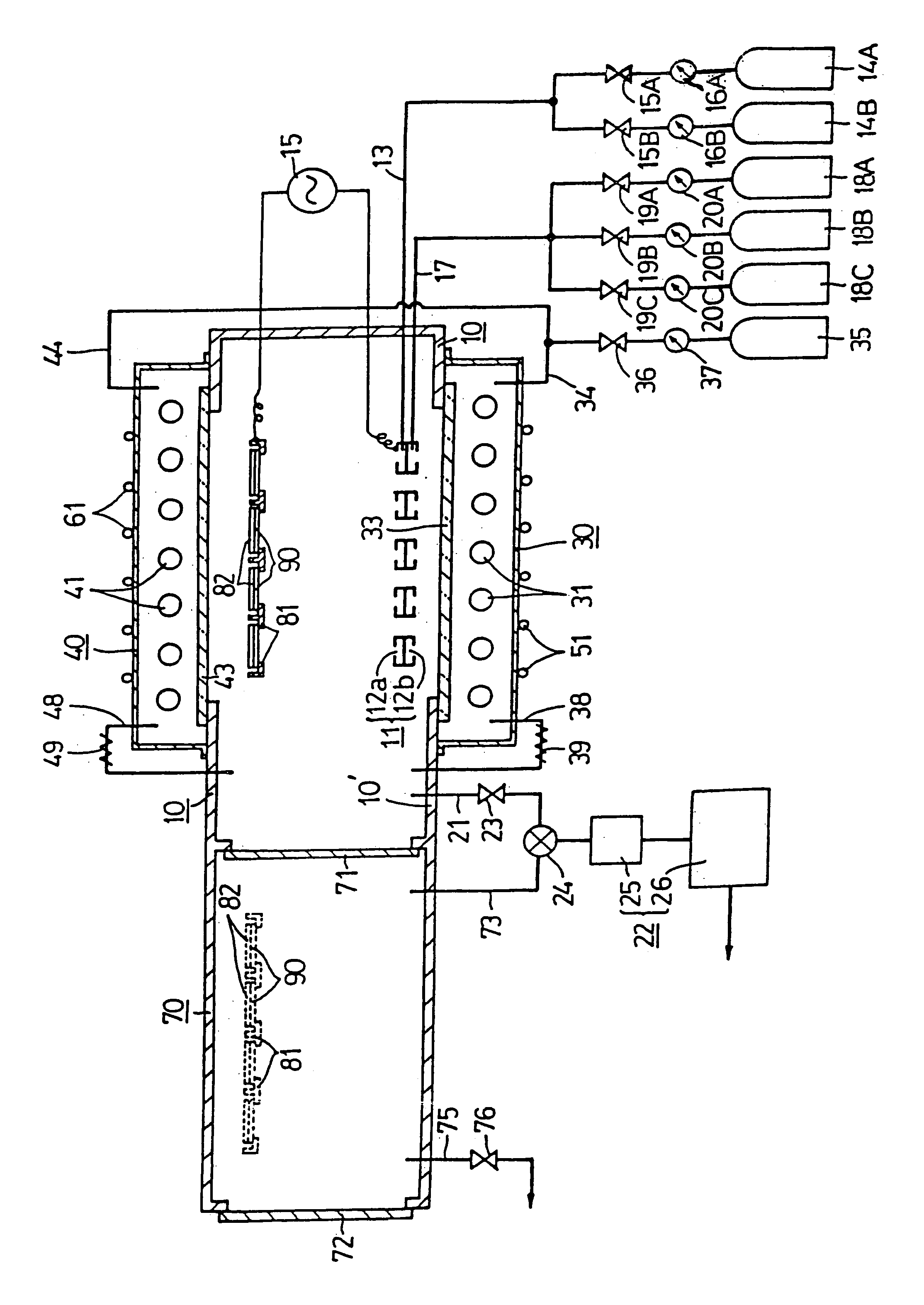

[0039]A description will given of a first embodiment of the present invention for forming the layer member as a insulating layer member on the substrate member 90.

[0040](1) The shutter means 71 between the reaction chamber 10 and the substrate take-in / take-out chamber 70, the shutter means 72 of the chamber 70 a valve 76 between the chamber 70 and the outside, the valves 15A and 15B between the nozzle parts 12a and the gas sources 14A and 14B, the valve 19A, 19B and 19C between the nozzle parts 12b and the gas sources 18A, 18B and 18C and the valve 36 between the chambers 30 and 40 and the gas source 35 are closed.

[0041](2) Next, the valve 23 between the reaction chamber 10 and the vacuum pump system 22 is opened and change-over valve 24 is also opened to the both chambers 10, 70, 30 and 40 to a pressure of 10−7 Torr.

[0042](3) Next, the turbo pump 25 and the rotary pump 26 of the vacuum pump system 22 are activated, evacuating the chambers 10 and 70.

[0043](4) Next, the valve 23 is c...

embodiment 2

[0071]Next, a description will be given of a second embodiment of the present invention for forming a semiconductor layer member as a layer member on a substrate.

[0072]This embodiment forms an amorphous silicon layer as the semiconductor layer member on the substrate 90 by the same steps as those in Embodiment 1 except the following steps.

[0073](12′) In step (12) in Embodiment 1 the heating temperature of the substrate 90 is changed from 350 C to 250 C.

[0074](14′) In step (14) of Embodiment 1 only the disilane (Si2H6) gas is introduced into the chamber 10 and the pressure in the chamber 10 is changed from 3 Torr to 2.5 Torr. A first amorphous silicon layer is deposited as a first semiconductor layer on the substrate 90.

[0075](15′) In step (15) of Embodiment 1, when the first amorphous silicon layer, instead of the first silicon nitride layer, is deposited about 1000 A thick on the substrate member 90, the disilane is discharged or excited into a plasma in place of the gas mixture of...

embodiment 3

[0077]Next, a description will be given of a third embodiment of the present invention which forms an aluminum nitride (AlN) layer member as a insulating layer member on a substrate.

[0078]Embodiment 3 employs a same steps as those in Embodiment 1 except the following steps.

[0079](14′) In step (14) of Embodiment 1 methyl aluminum (Al(CH3)3), instead of the disilane, is introduced from the gas source 14A into the chamber 10, whereby a first aluminum nitride (AlN) layer is deposited as a first insulating layer on the substrate 90. In this case, the deposition rate of the first aluminum nitride layer is 230 A / min.

[0080](15′) In step (15) of Embodiment 1 a second aluminum nitride layer, instead of the second silicon nitride layer, is deposited on the first aluminum nitride layer.

[0081]While in the foregoing the present invention has been described in connection with the cases of forming an insulating layer member having two insulating layers of the same material and a semiconductor layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com