Logic device and method supporting scan test

a logic device and scan technology, applied in the field of scan testing systems and methods, can solve the problems of reducing the performance of the logic circuit, consuming more power during normal non-test operation, and consuming less power during pulsed latches, so as to reduce the delay in the data path, reduce the delay, and consume less power.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

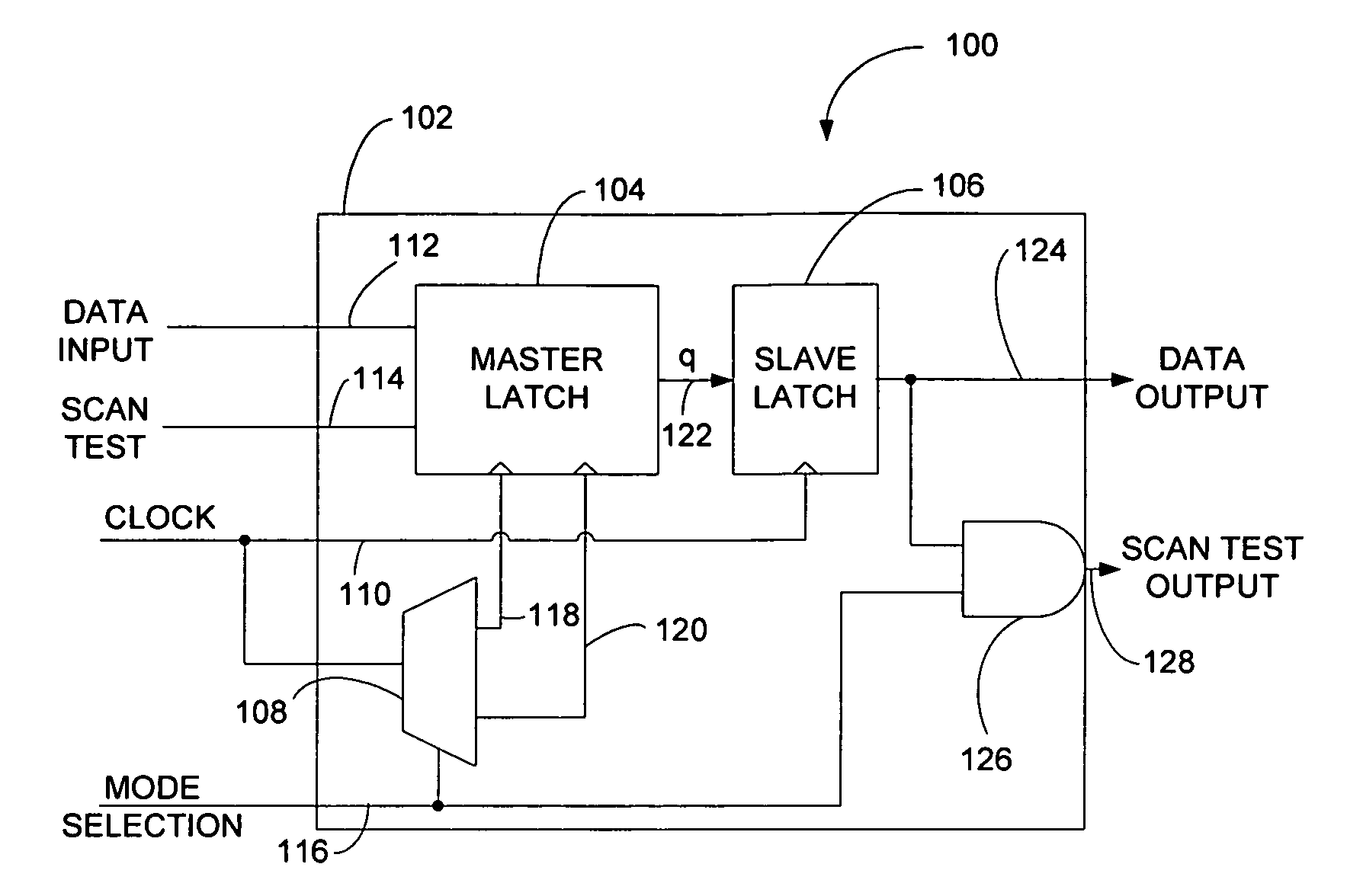

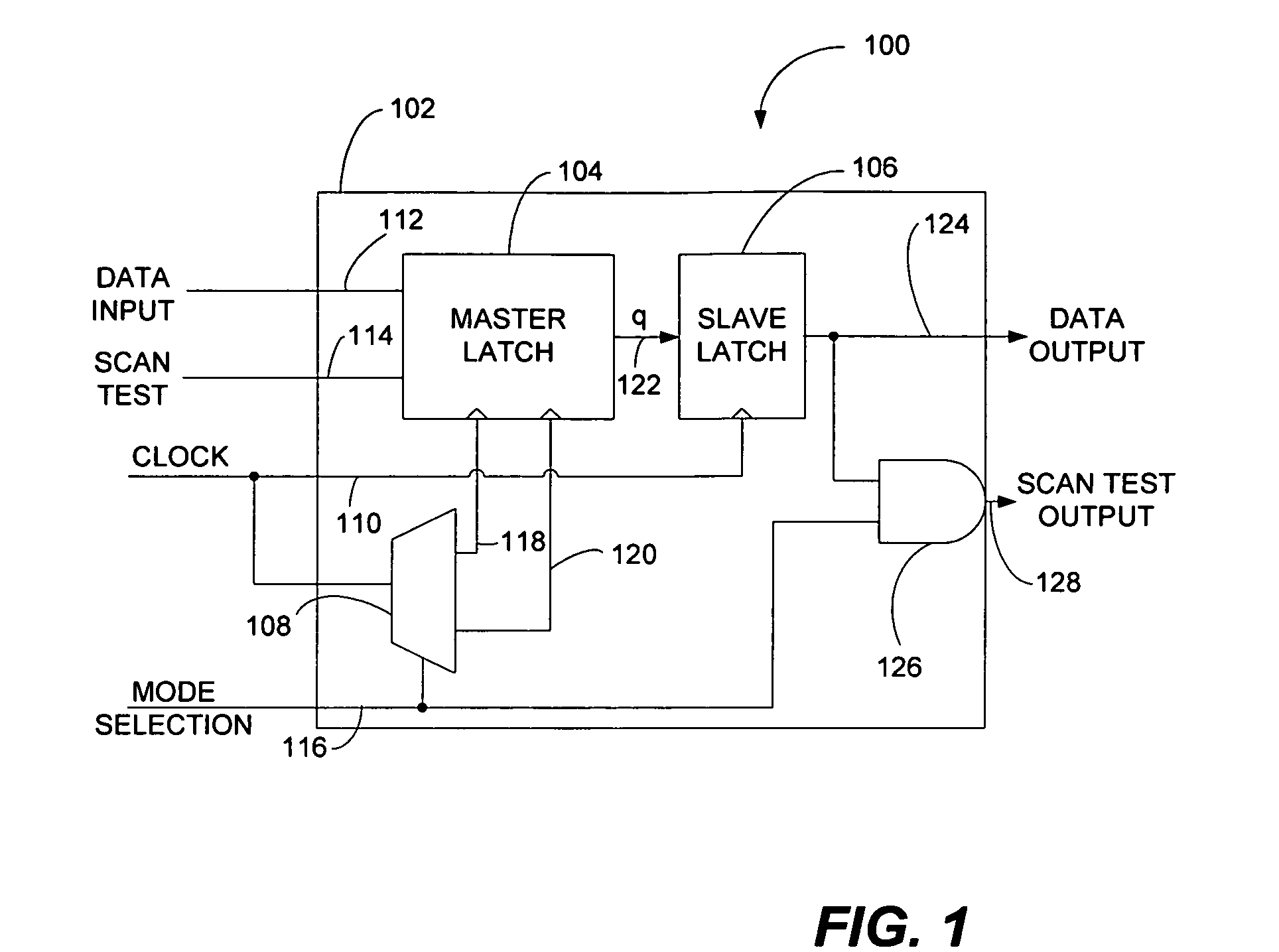

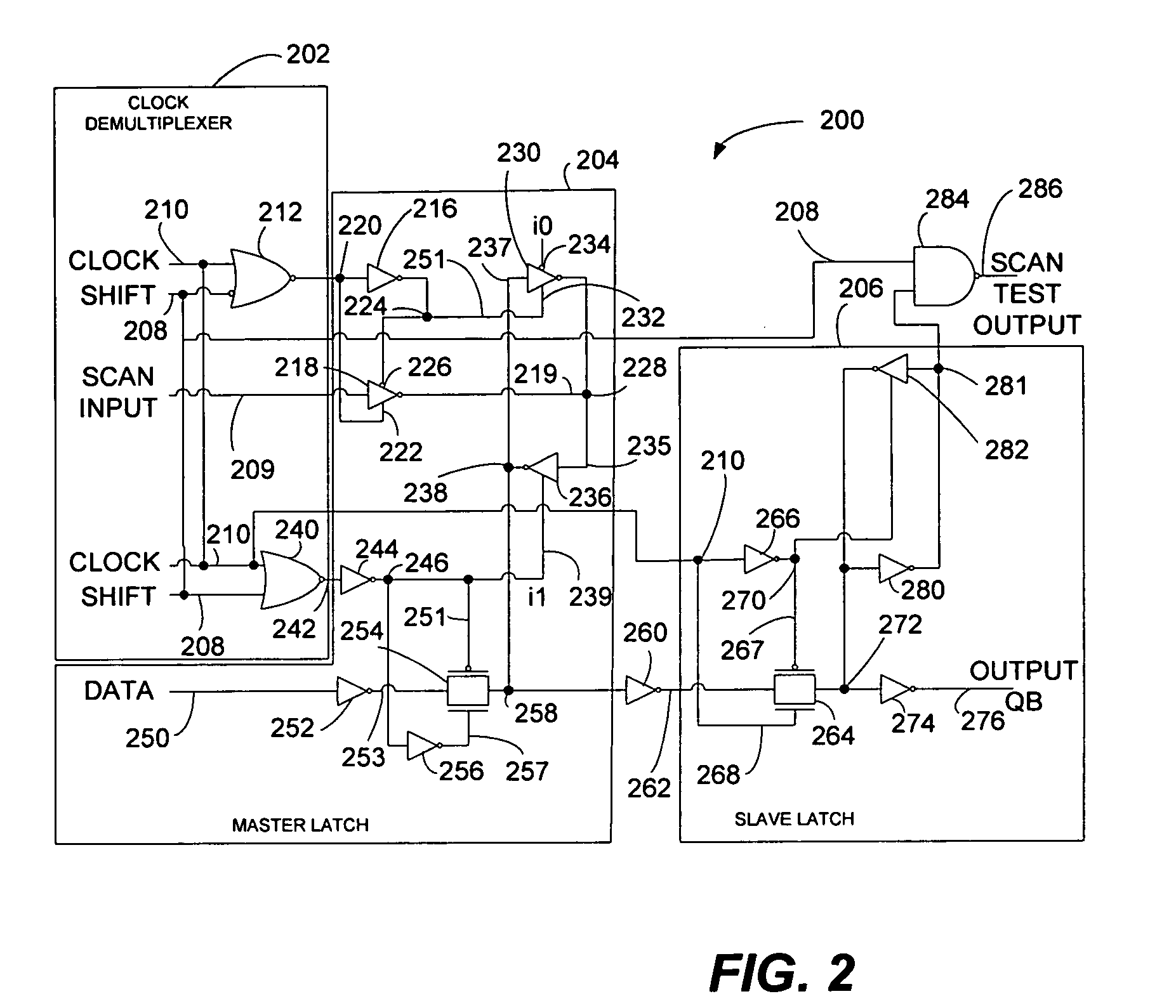

[0023]FIG. 1 is a block diagram of a logic device 100 with design for testability (DFT) compatible test logic. The logic device 100 includes an integrated circuit 102 that includes a master latch 104, a slave latch 106, and a clock demultiplexer 108. The integrated circuit 102 includes a clock input 110, a data input 112, a scan test input 114, and a mode selection input 116. The clock demultiplexer 108 receives the clock input 110 and a mode selection input 116. The clock demultiplexer 108 is responsive to the clock input 108 to selectively provide a first clock output 118 and a second clock output 120. The master latch 104 is coupled to the data input 112 and to the scan test input 114. The master latch 104 also includes an output 122. The master latch 104 is responsive to the first clock output 118 of the clock demultiplexer 108 and the second clock output 120 of the clock demultiplexer 108 to selectively couple the data input 112 or the scan test input 114 to the output 122. In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com