Evaluation of a temporal description within a general purpose programming language

a general purpose programming language and temporal description technology, applied in the field of hardware functional verification, can solve the problems that the ordinal execution mechanism provided by general purpose programming language compilers cannot handle such a situation, and the language syntax cannot be easily changed to support hardware simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

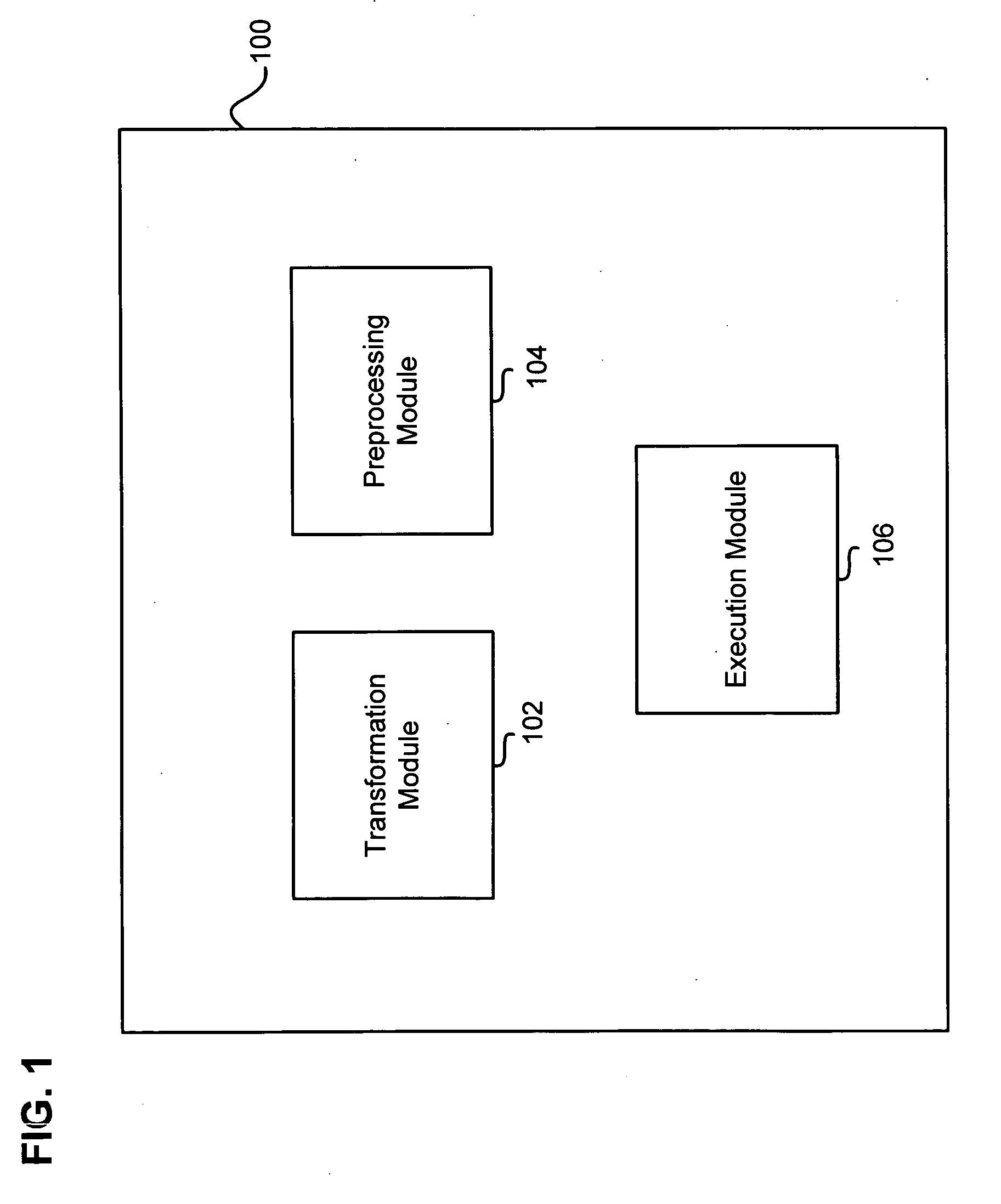

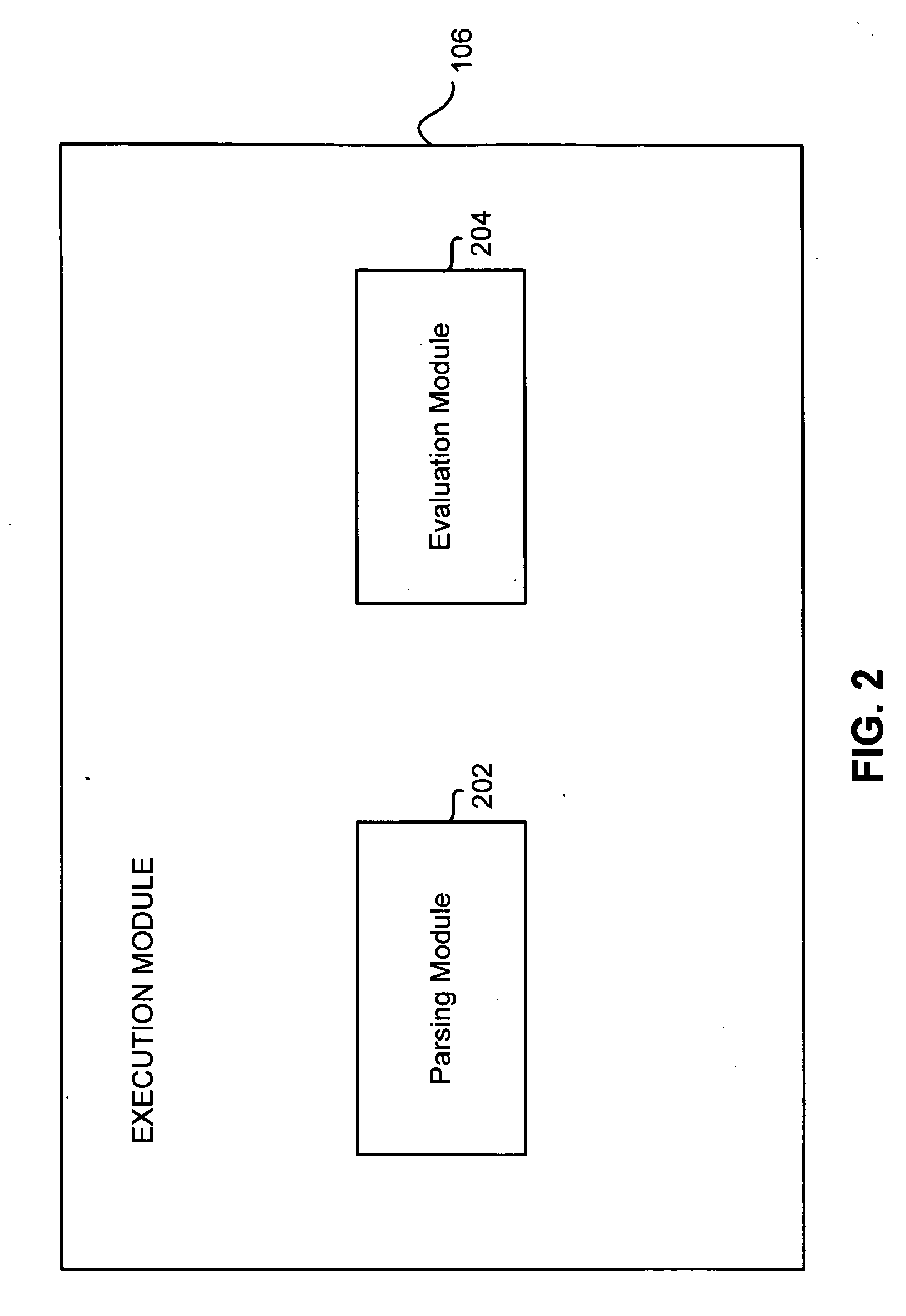

[0020]FIG. 1 is a high-level block diagram of a computing environment 100 according to an embodiment of the present invention. FIG. 1 illustrates that the computing environment 100 includes a transformation module 102 (generally referred to as a translation module), a preprocessing module 104 (also generally referred to as a translation module), and an execution module 106. Those of skill in the art will understand that other embodiments of the computing environment 100 can have different and / or other modules than the ones described herein. In addition, the functionalities can be distributed among the modules in a manner different than described herein.

[0021] In an embodiment of the invention, a temporal description is written within a general purpose programming language such as C++. The temporal description can be expressed with either an extended syntax or a preprocessor macro. In the case of an extended syntax, the transformation module 102 (e.g., a parser program or a compiler...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com