Method and apparatus for wiring, wire, and integrated circuit

a technology of integrated circuits and wires, applied in the direction of solid-state devices, coatings, chemical vapor deposition coatings, etc., can solve the problems of increasing interconnection resistance, difficulty in sufficiently plugging the wiring material, and conventional plugging methods not working sufficiently

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In the following, one embodiment according to the invention will be described when applied to a producing process of an integrated circuit (hereinafter, referred to as "IC"), for example. can be divided into "front-end process" and "back-end process". "Front-end process" is a process for providing an IC element on the wafer. On the other hand, "back-end process" is a process for electrically connecting the IC elements on the wafer. The present invention can be applied to the "backend process".

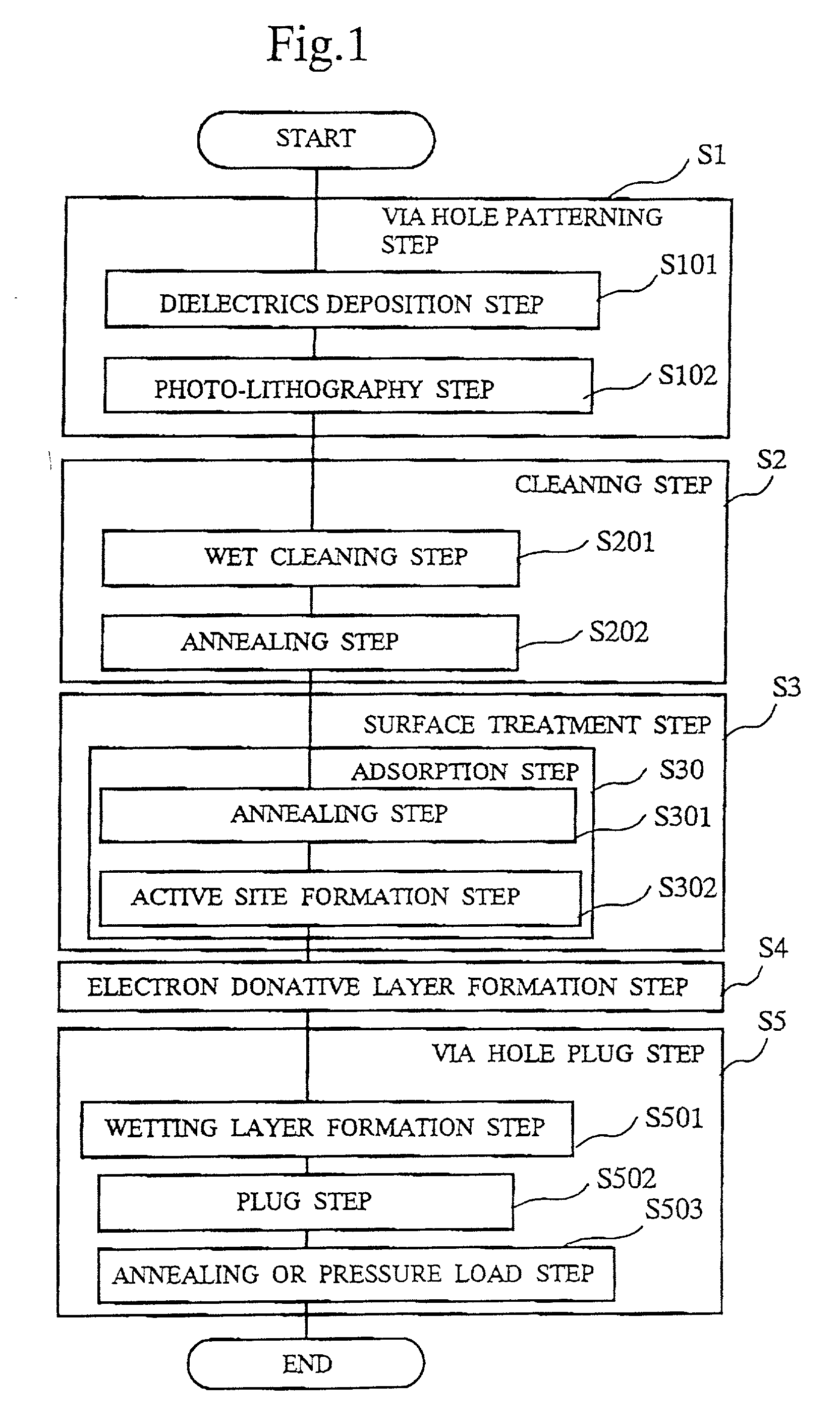

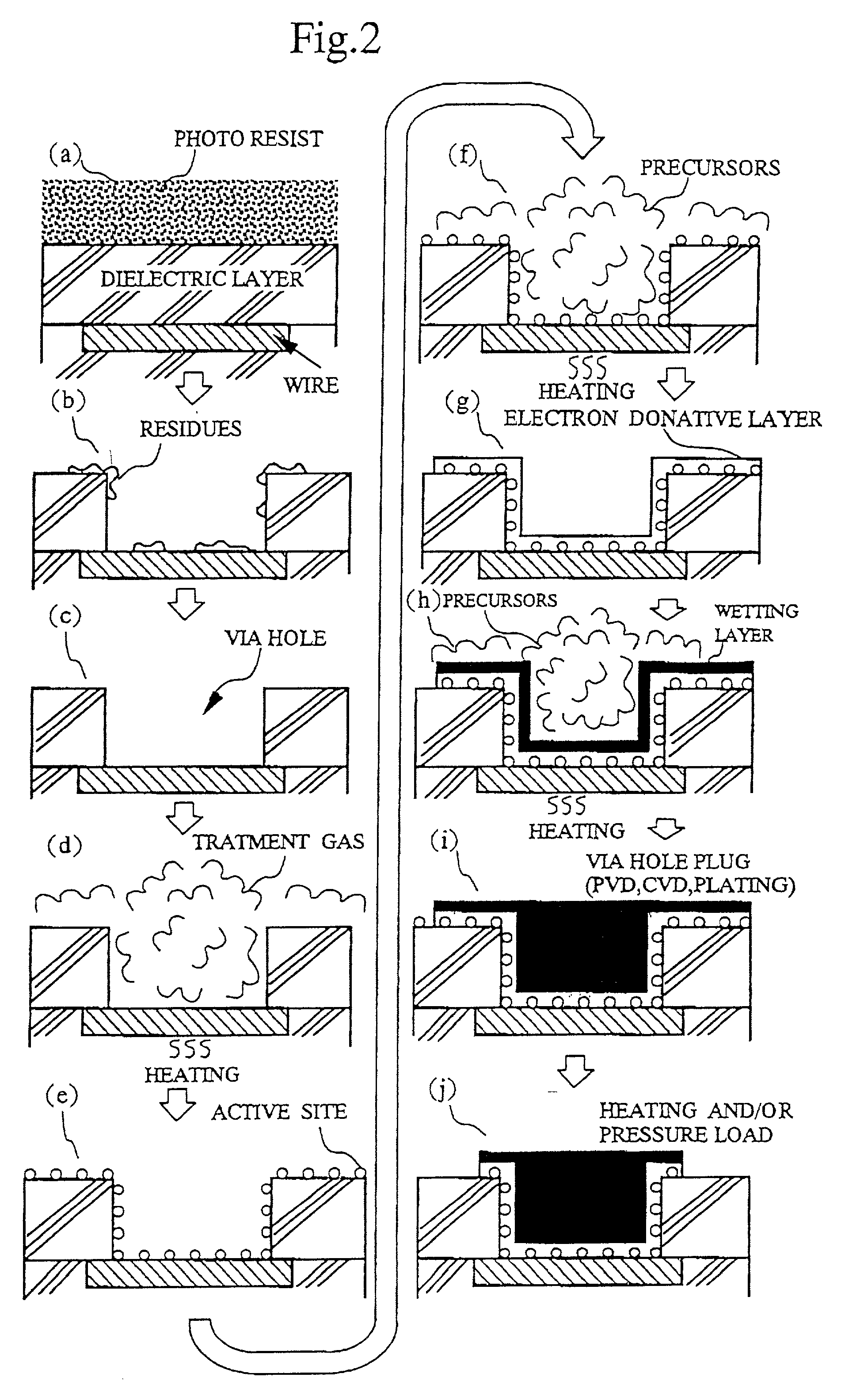

[0027] As shown in FIG. 1, the embodiment according to the invention is performed after a via hole patterning step S1 and a cleaning step S2. The via hole patterning step S1 is provided for producing the via hole in a dielectric layer (a film of dielectronics). Secondly, the cleaning step S2 is provided for removing soil on the wafer such as contaminant and impurities remained after the via hole is patterned.

[0028] The via hole patterning step S1 includes a dielectrics deposition step S1...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Density | aaaaa | aaaaa |

| Affinity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com