Analog to digital signal conditioning in optoelectronic transceivers

An optoelectronic transceiver, analog signal technology, applied in electromagnetic transceivers, electrical components, electromagnetic wave transmission systems, etc., can solve problems such as adverse effects of measurement accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

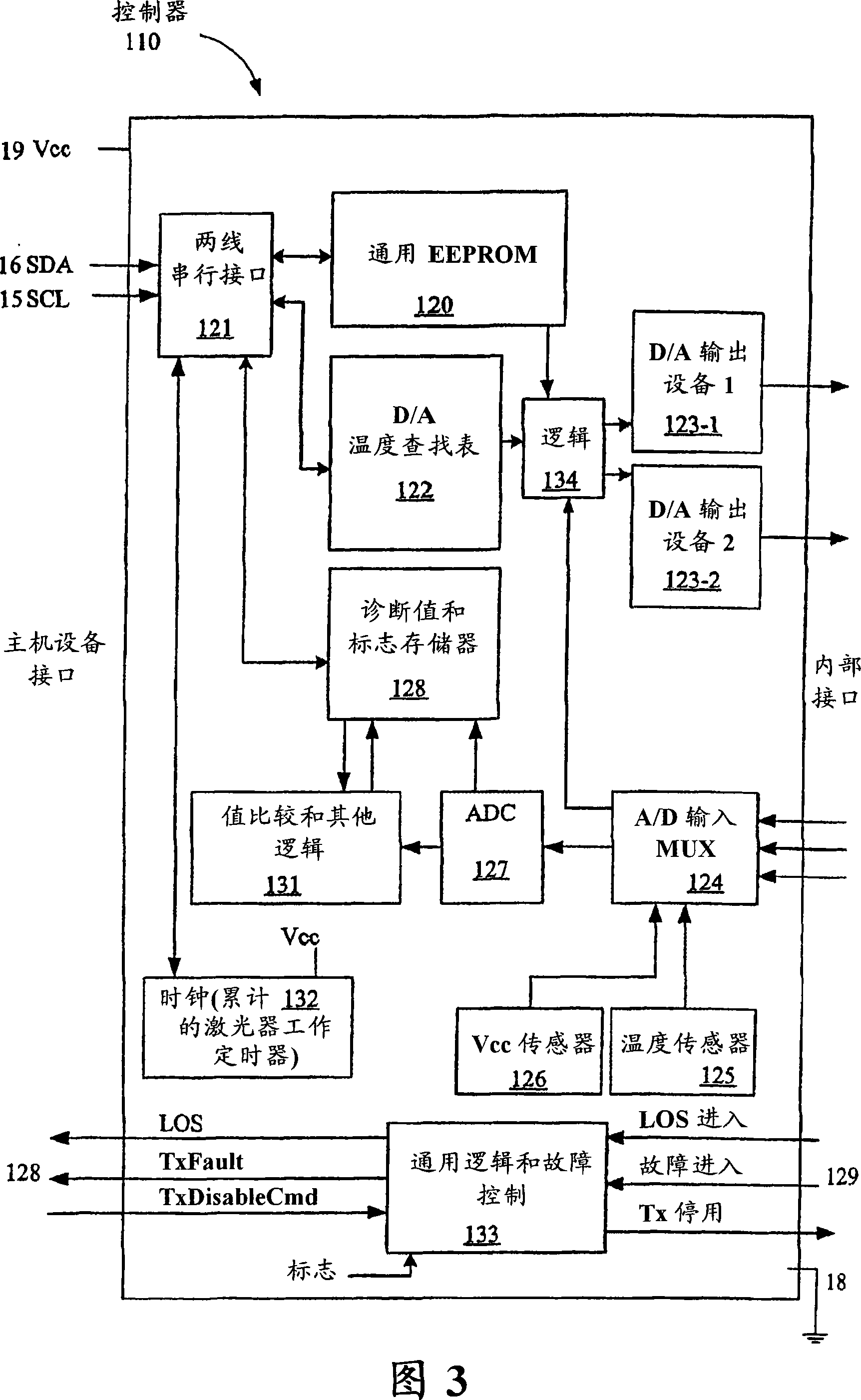

[0092] The power monitor 422 (FIG. 4) in the fiber optic transceiver includes the power monitor or its associated circuitry, and when it fails, it will indicate no or very low power output even if the laser is operating. The laser bias driver will attempt to increase the output power of the transmitter by increasing the laser bias current. Since the feedback is interrupted, the laser is driven to its maximum emission capability, which may exceed the eye safety alarm set point. A fast-trip alarm flag is generated within 10 microseconds of the fault and is used to shut down the laser driver via the internal Tx disable (Dout) output. A high-resolution alarm for laser bias current is generated and a high-resolution low alarm for power is also present if the fast-trip alarm fails or is not selected in the output logic settings, and either Both can be used to shut down the laser driver and / or TOSA.

example 2

[0094] When the laser driver (in all types of fiber optic transceivers) or its associated circuitry fails, the laser will be driven to its maximum output. Depending on the particular fault, the laser's bias current reading may be zero or very high, and, in fiber optic transceivers that include a power monitor, the power reading will be high. Within 10 microseconds, a fast-trip alarm for laser bias current and a fast-trip alarm for transmitted output power will generate an alarm flag. A high-resolution low alarm for laser bias current will generate an alarm flag if the laser bias current reading is zero. This may not be distinguishable from faults that result in zero light output (such as an open circuit in the laser line or a short circuit in the laser), however, safety considerations allow the alarm system to err on the side of this and command the laser to shut down. In this case, the logic cannot physically shut down the laser if the failure is caused by a shorted bias dri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com