System for testing clock signal dither and method thereof

A clock signal, system-on-chip technology, applied in electronic circuit testing, automatic power control, electrical components, etc., can solve problems such as long test time, variable delay line linearity limitation, etc., to achieve the effect of unilateral delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be described in further detail below in conjunction with the accompanying drawings.

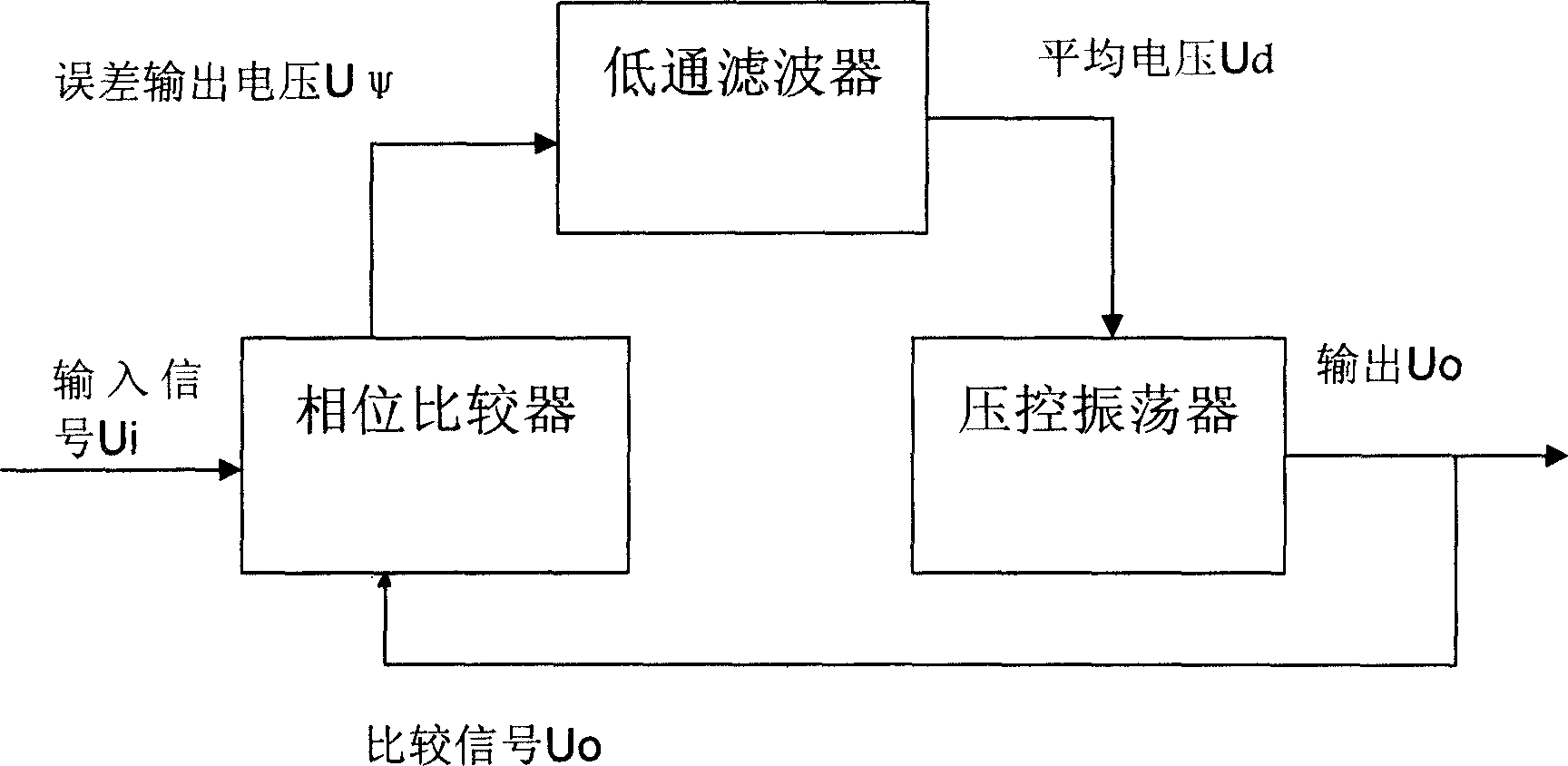

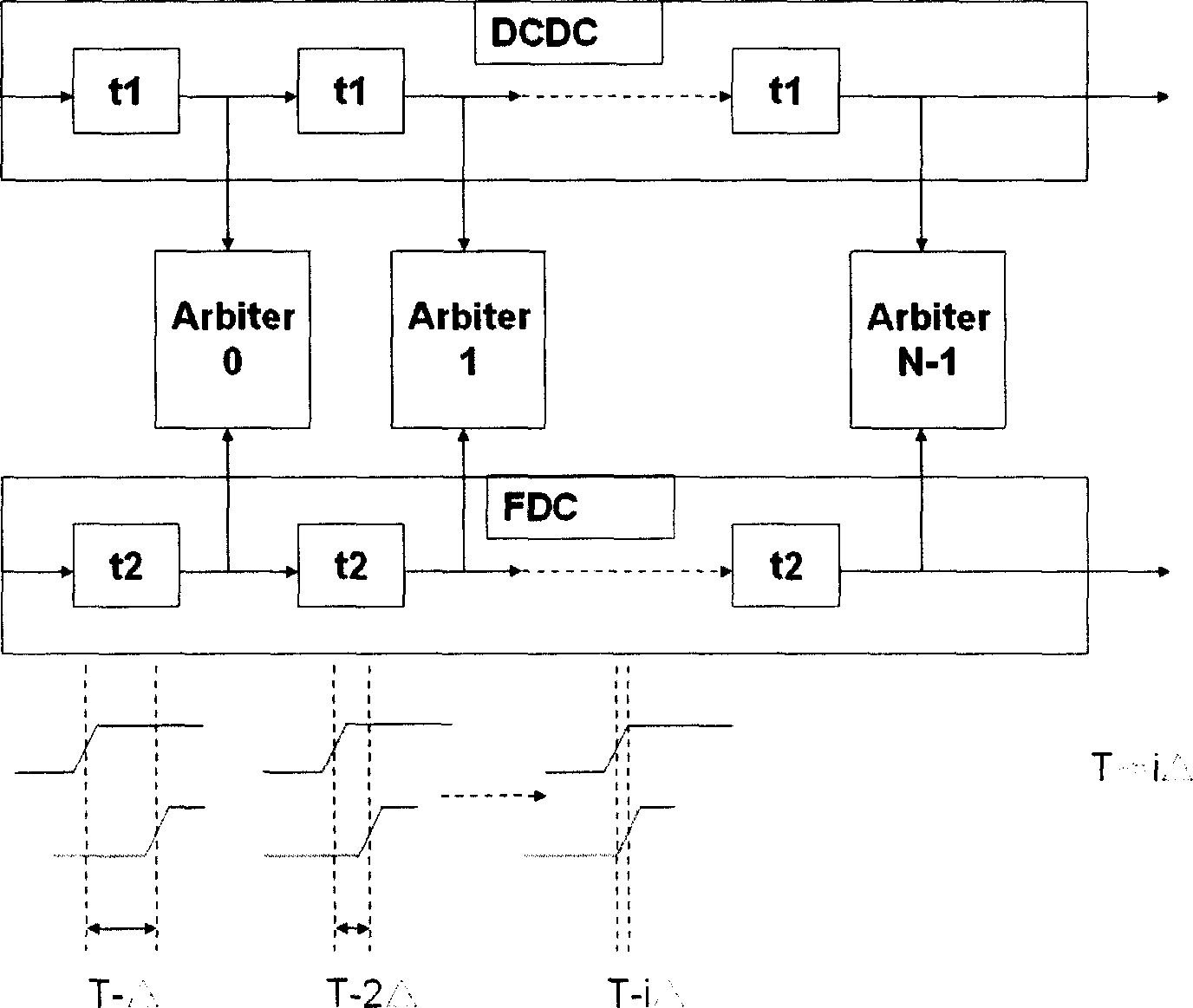

[0045] The present invention adopts the Vernier Delay line measurement method to measure the jitter of the clock signal, and the present invention realizes the Vernier Delay line measurement method by adopting an analog controllable unilateral delay line. The so-called unilateral delay refers to controlling the delay line so that the rising edge of the clock passing through the delay line is retreated, while the falling edge only moves a little.

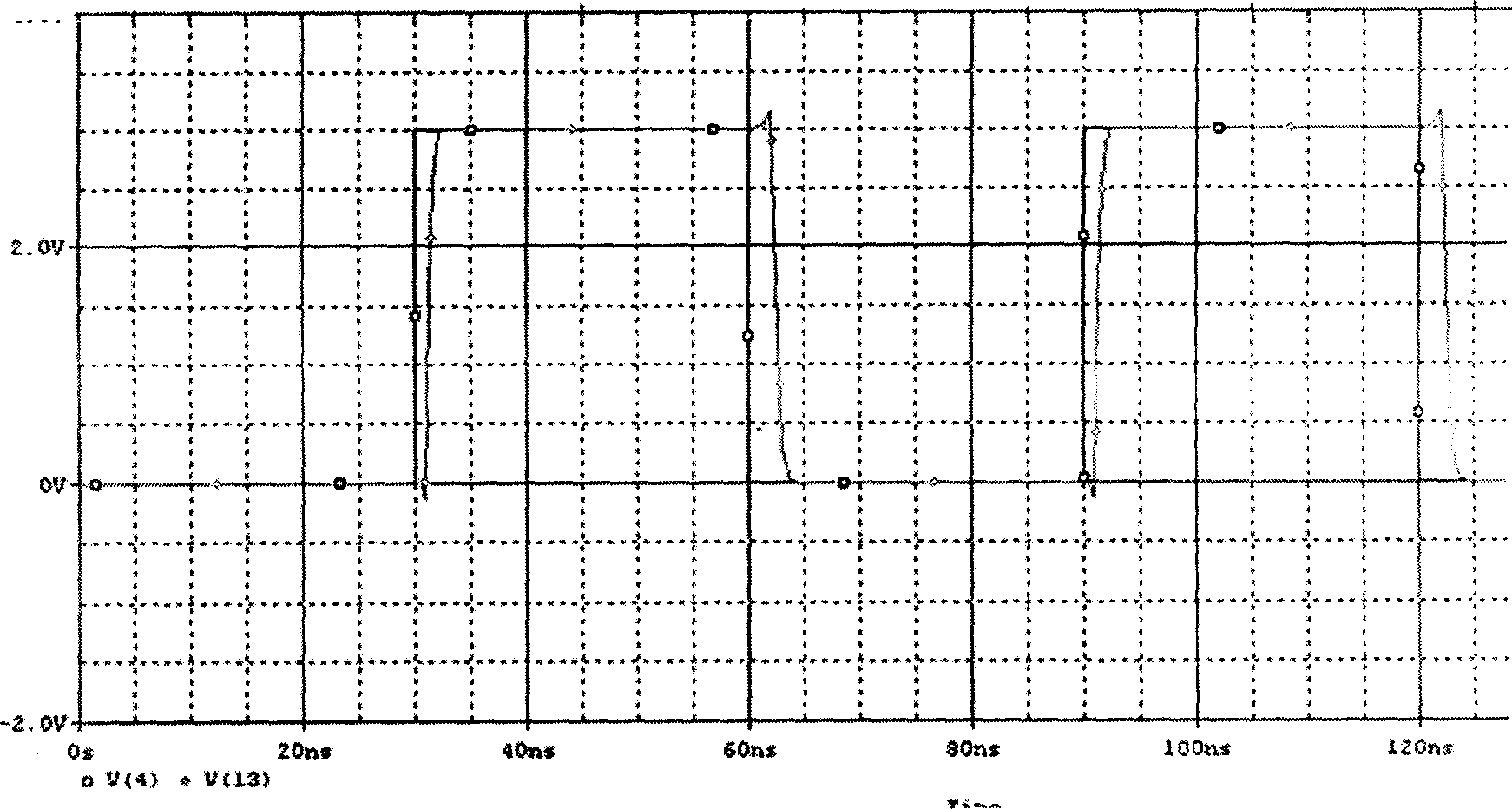

[0046] Such as Figure 3A , 3B , 3C, and 3D are the delay results of the unilateral delay line of the present invention under different control conditions of Vcontrol. The line with hollow dots in the figure is the reference clock, while the line with solid dots is the delay result with different Vcontrol delays. Fig. 3 is the result of a schematic experiment about unilateral delay control, the experiment adopts ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com