Synchronous dynamic storage controller designing method

A technology of synchronous dynamics and design methods, applied in the direction of static memory, digital memory information, information storage, etc., to achieve the effect of improving utilization rate, satisfying high-speed communication, and reducing command pipeline conflicts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

[0021] The specific implementation of the present invention on SDRAM is as follows, and the implementation on DDR SDRAM is similar to SDRAM.

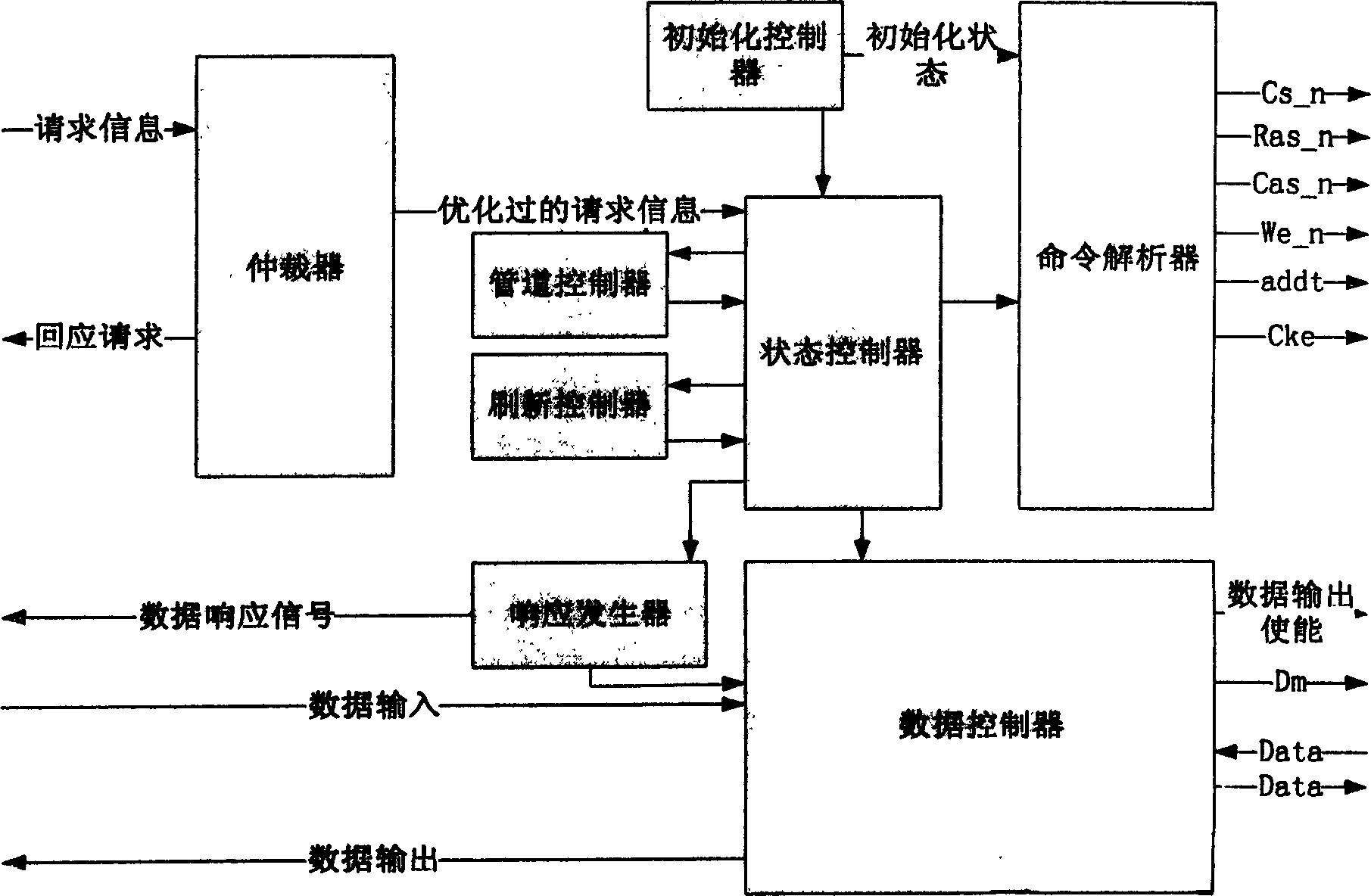

[0022] 1. Technical solution of SDRAM controller

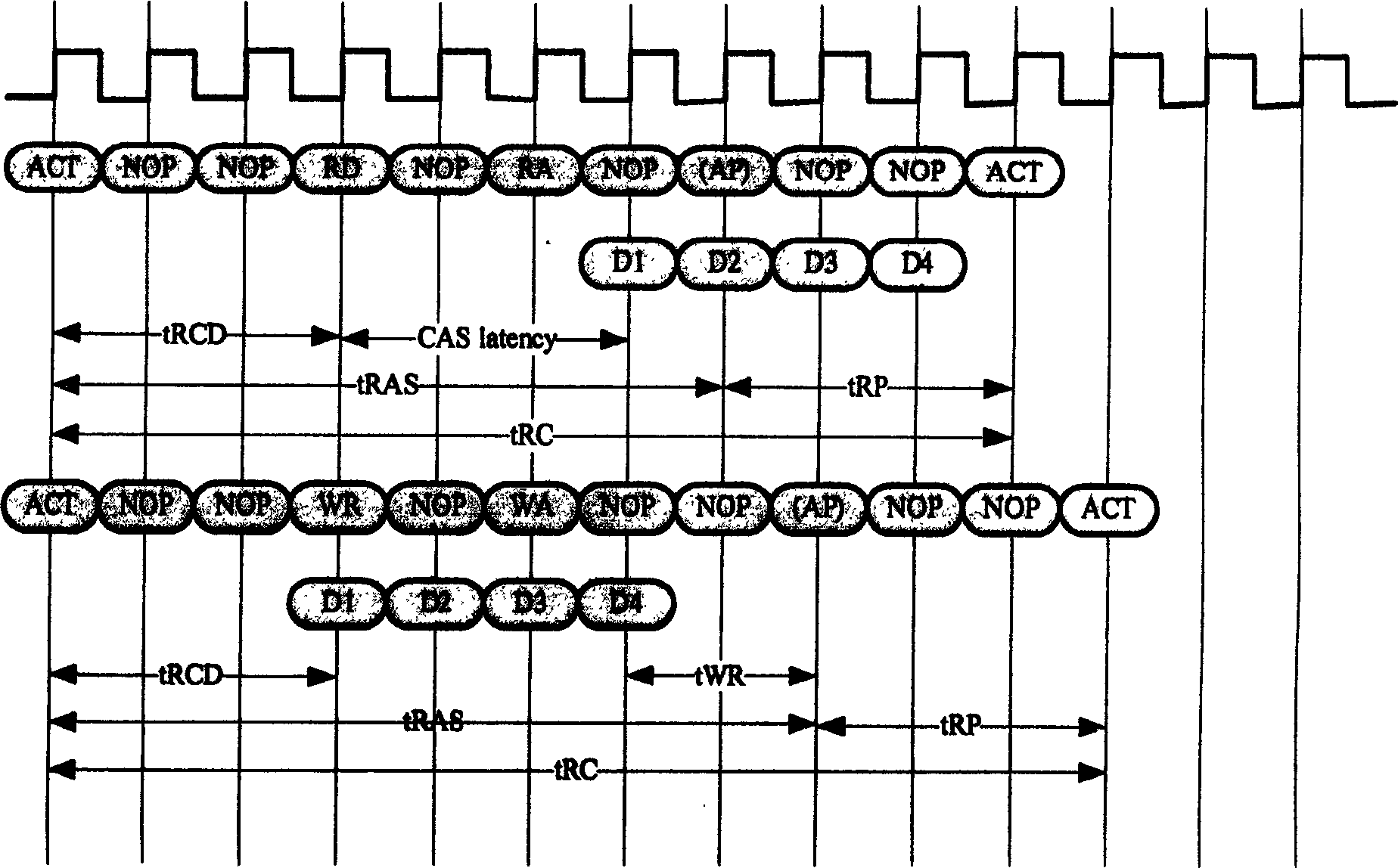

[0023] Such as figure 1 As shown, according to the specification of SDRAM, to read and write any data on SDRAM, it must first be activated to open the row where it is located, and then read and write. After the read and write is completed, the row needs to be pre-charged to close the row. In order to get a data, additional time tRCD and tRP must be added to open and close the row where the data is located, and the whole process is also limited by tRC and tRAS.

[0024] There are 4 relatively independent banks in SDRAM. After the initialization operation is completed, except for commands such as refresh (Refresh) and reset register (LMR), each bank is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com