Apparatus and method for testing conductive bumps

A technology of conductive bumps and testing devices, which is used in measurement devices, semiconductor/solid-state device testing/measurement, and single semiconductor device testing, etc., can solve problems such as labor time-consuming, unsuitable for product wafer testing and evaluation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

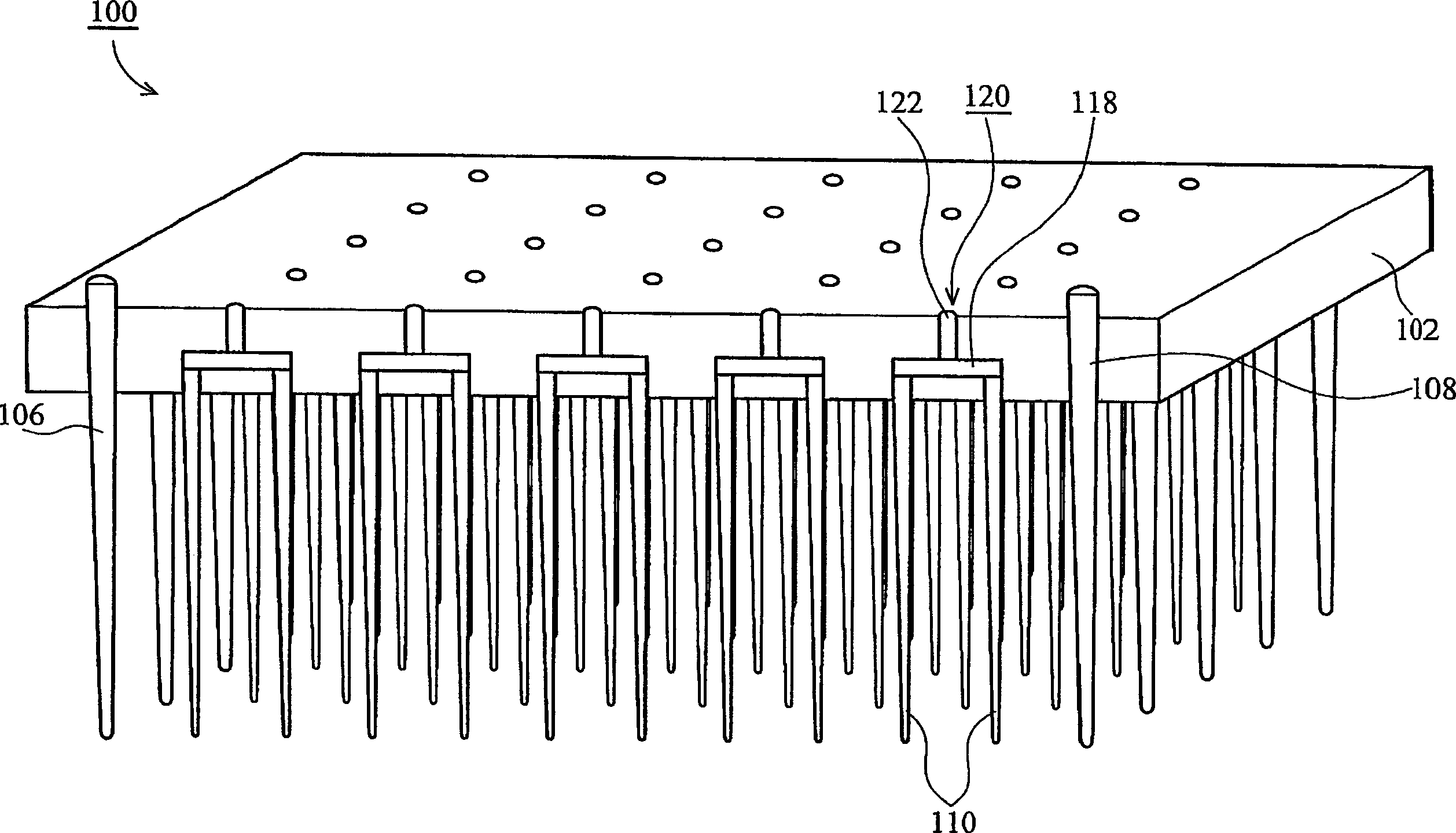

[0031] In order to make the above and other objects, features and advantages of the present invention more comprehensible, a preferred embodiment is specifically cited below, together with the accompanying drawings, and is described in detail as follows:

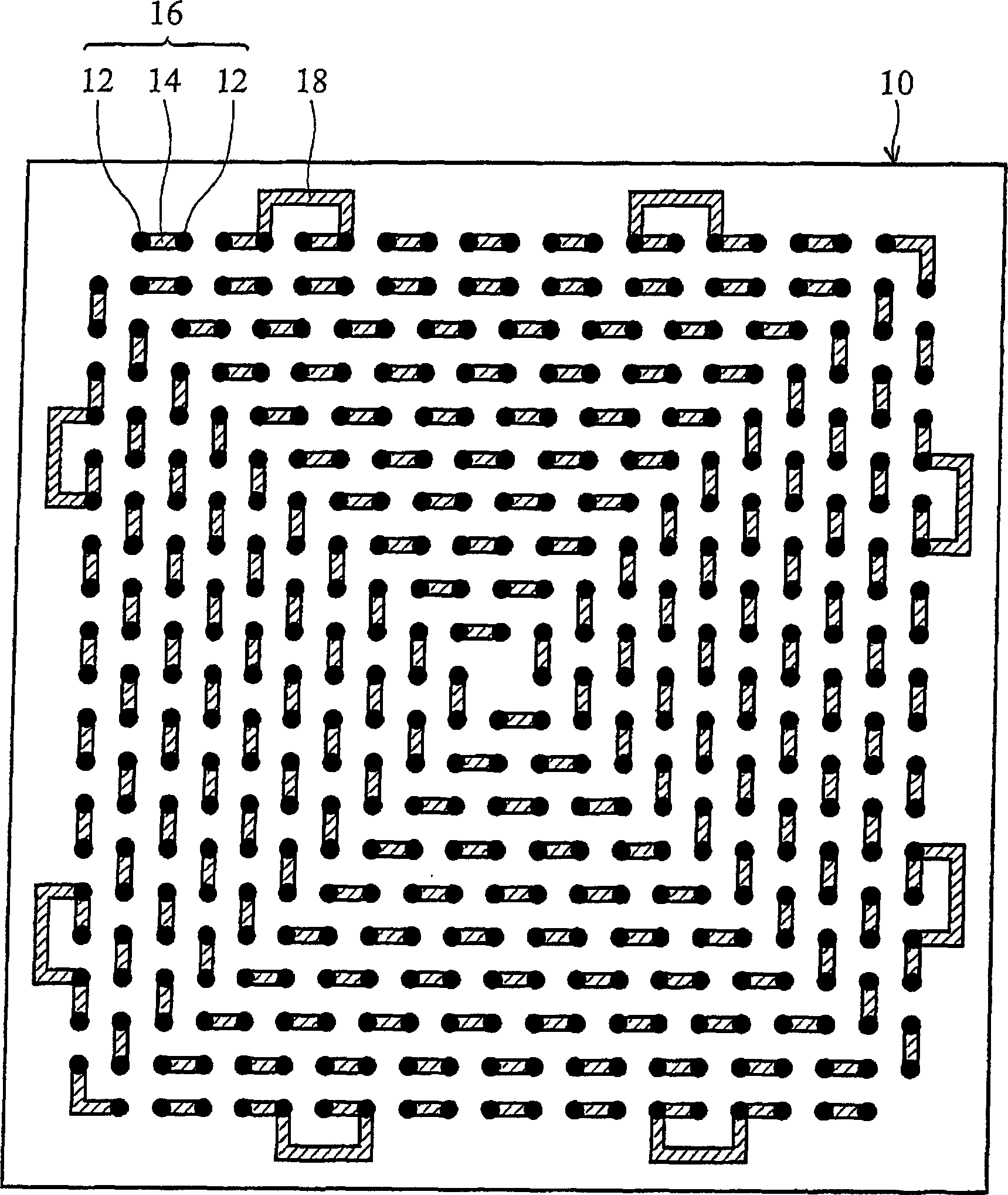

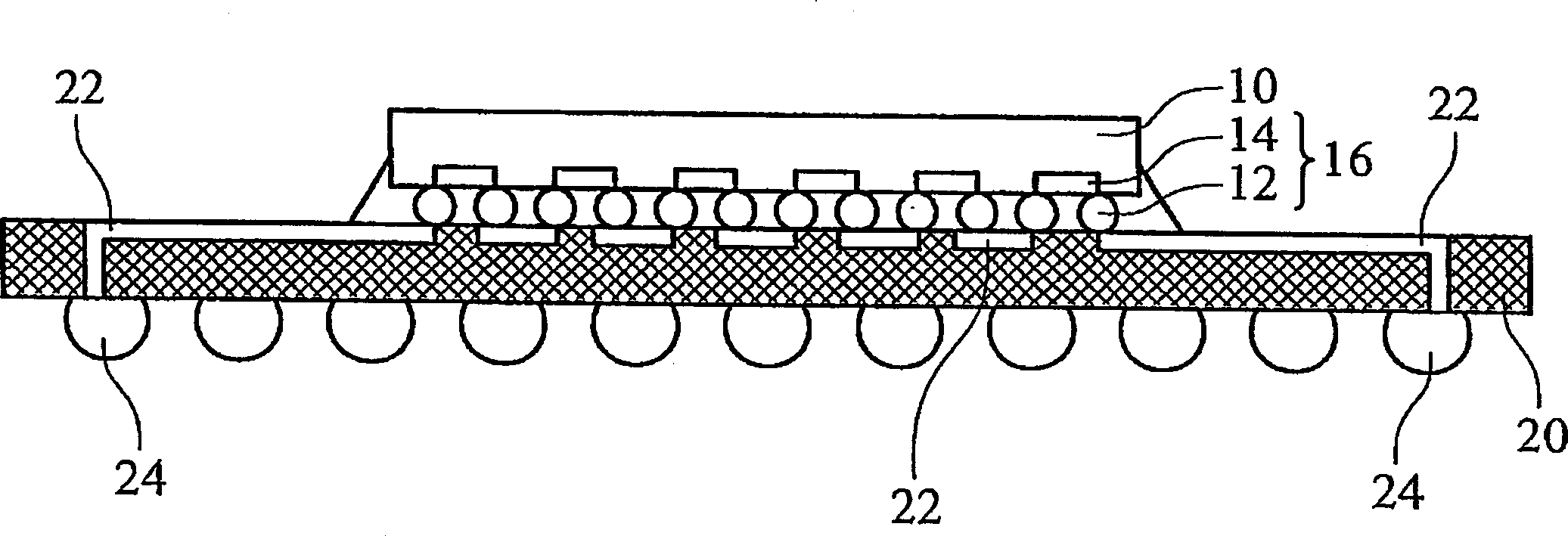

[0032] Embodiments of the invention will Figure 3 to Figure 7 Make a detailed description as follows. Figure 3 to Figure 6 is a series of schematic diagrams for illustrating a conductive bump testing device according to an embodiment of the present invention, and Figure 7 It is a flowchart for illustrating a conductive bump testing method according to an embodiment of the present invention.

[0033] Please refer to image 3 , illustrates an apparatus 100 for testing conductive bumps. Here, the device 100 includes a support substrate 102 in which a plurality of test probes are formed. The support substrate 102 includes an insulating material such as ceramic material, epoxy, resin, polyimide, FR4 glass fiber, or polymer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com